Page

### Inter-Integrated Circuit Module (I2C)

This chapter describes the features and operation of the inter-integrated circuit (I2C) module. The I2C module provides an interface between one of these devices and devices compliant with the NXP Semiconductors Inter-IC bus (I2C bus) specification version 2.1, and connected by way of an I2C bus. External components attached to this 2-wire serial bus can transmit/receive 1 to 8-bit data to/from the device through the I2C module. This guide assumes the reader is familiar with the I2C bus specification.

#### Topic

| 20.1 | Introduction                                   | 2302 |

|------|------------------------------------------------|------|

| 20.2 | Configuring Device Pins                        | 2305 |

| 20.3 | I2C Module Operational Details                 | 2306 |

| 20.4 | Interrupt Requests Generated by the I2C Module | 2313 |

| 20.5 | Resetting or Disabling the I2C Module          | 2316 |

| 20.6 | I2C Registers                                  | 2317 |

|      | -                                              |      |

**NOTE:** A unit of data transmitted or received by the I2C module can have fewer than 8 bits; however, for convenience, a unit of data is called a data byte throughout this document. The number of bits in a data byte is selectable via the BC bits of the mode register, I2CMDR.

#### 20.1 Introduction

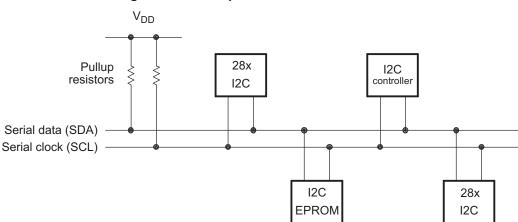

The I2C module supports any slave or master I2C-compatible device. Figure 20-1 shows an example of multiple I2C modules connected for a two-way transfer from one device to other devices.

#### Figure 20-1. Multiple I2C Modules Connected

#### 20.1.1 Features

The I2C module has the following features:

- Compliance with the NXP Semiconductors I2C bus specification (version 2.1):

- Support for 8-bit format transfers

- 7-bit and 10-bit addressing modes

- General call

- START byte mode

- Support for multiple master-transmitters and slave-receivers

- Support for multiple slave-transmitters and master-receivers

- Combined master transmit/receive and receive/transmit mode

- Data transfer rate from 10 kbps up to 400 kbps (Fast-mode)

- Receive FIFO and Transmitter FIFO (16-deep x 8-bit FIFO)

- Supports two ePIE interrupts:

- I2Cx Interrupt Any of the below events can be configured to generate an I2Cx interrupt:

- Transmit-data ready

- Receive-data ready

- Register-access ready

- No-acknowledgment received

- Arbitration lost

- Stop condition detected

- Addressed as slave

- I2Cx\_FIFO interrupts:

- Transmit FIFO interrupt

- Receive FIFO interrupt

- Module enable/disable capability

- Free data format mode

#### 20.1.2 Features Not Supported

The I2C module does not support:

- High-speed mode (Hs-mode)

- CBUS-compatibility mode

#### 20.1.3 Functional Overview

Each device connected to an I2C bus is recognized by a unique address. Each device can operate as either a transmitter or a receiver, depending on the function of the device. A device connected to the I2C bus can also be considered as the master or the slave when performing data transfers. A master device is the device that initiates a data transfer on the bus and generates the clock signals to permit that transfer. During this transfer, any device addressed by this master is considered a slave. The I2C module supports the multi-master mode, in which one or more devices capable of controlling an I2C bus can be connected to the same I2C bus.

For data communication, the I2C module has a serial data pin (SDA) and a serial clock pin (SCL), as shown in Section 20.6. These two pins carry information between the 28x device and other devices connected to the I2C bus. The SDA and SCL pins both are bidirectional. They each must be connected to a positive supply voltage using a pull-up resistor. When the bus is free, both pins are high. The driver of these two pins has an open-drain configuration to perform the required wired-AND function.

There are two major transfer techniques: .

- Standard Mode: Send exactly n data values, where n is a value you program in an I2C module register. See Section 20.6 for more information.

- Repeat Mode: Keep sending data values until you use software to initiate a STOP condition or a new START condition. See *Registers* for RM bit information.

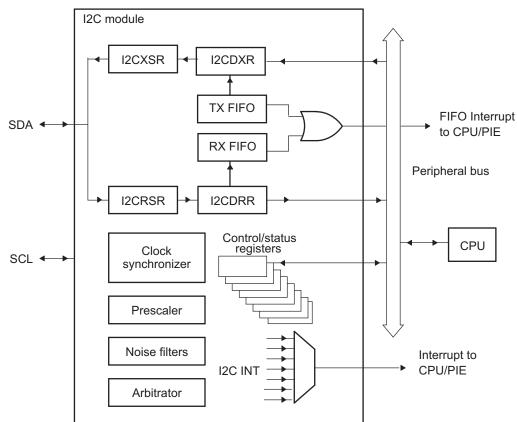

The I2C module consists of the following primary blocks:

- A serial interface: one data pin (SDA) and one clock pin (SCL)

- Data registers and FIFOs to temporarily hold receive data and transmit data traveling between the SDA pin and the CPU

- Control and status registers

- A peripheral bus interface to enable the CPU to access the I2C module registers and FIFOs.

- A clock synchronizer to synchronize the I2C input clock (from the device clock generator) and the clock on the SCL pin, and to synchronize data transfers with masters of different clock speeds

- A prescaler to divide down the input clock that is driven to the I2C module

- A noise filter on each of the two pins, SDA and SCL

- An arbitrator to handle arbitration between the I2C module (when it is a master) and another master

- Interrupt generation logic, so that an interrupt can be sent to the CPU

- FIFO interrupt generation logic, so that FIFO access can be synchronized to data reception and data transmission in the I2C module

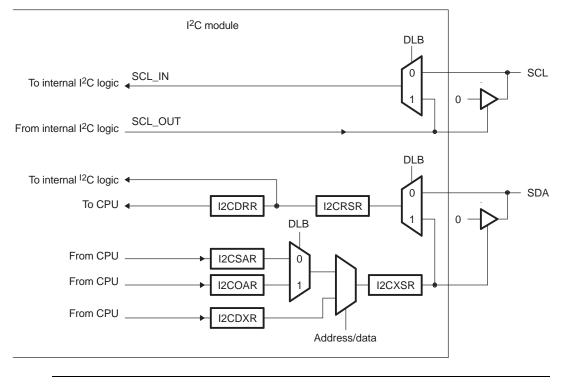

Figure 20-2 shows the four registers used for transmission and reception in non-FIFO mode. The CPU writes data for transmission to I2CDXR and reads received data from I2CDRR. When the I2C module is configured as a transmitter, data written to I2CDXR is copied to I2CXSR and shifted out on the SDA pin one bit at a time. When the I2C module is configured as a receiver, received data is shifted into I2CRSR and then copied to I2CDRR.

Figure 20-2. I2C Module Conceptual Block Diagram

#### 20.1.4 Clock Generation

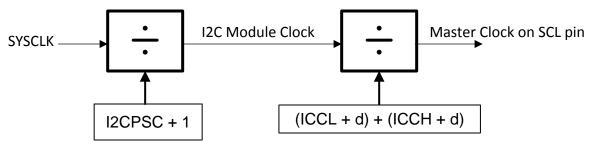

The I2C module clock determines the frequency at which the I2C module operates. A programmable prescaler in the I2C module divides down the SYSCLK to produce the I2C module clock and this I2C module clock is divided further to produce the I2C master clock on the SCL pin. Figure 20-3 shows the clock generation diagram for I2C module.

To specify the divide-down value, initialize the IPSC field of the prescaler register, I2CPSC. The resulting frequency is:

I2C Module Clock (Fmod) =

$$\frac{\text{SYSCLK}}{(\text{I2CPSC} + 1)}$$

**NOTE:** To meet all of the I2C protocol timing specifications, the I2C module clock must be between 7 - 12 MHz.

The prescaler must be initialized only while the I2C module is in the reset state (IRS = 0 in I2CMDR). The prescaled frequency takes effect only when IRS is changed to 1. Changing the IPSC value while IRS = 1 has no effect.

The master clock appears on the SCL pin when the I2C module is configured to be a master on the I2C bus. This clock controls the timing of communication between the I2C module and a slave. As shown in Figure 20-3, a second clock divider in the I2C module divides down the module clock to produce the master clock. The clock divider uses the ICCL value of I2CCLKL to divide down the low portion of the module clock signal and uses the ICCH value of I2CCLKH to divide down the high portion of the module clock signal. See Section 20.1.5 for the master clock frequency equation.

#### 20.1.5 I2C Clock Divider Registers (I2CCLKL and I2CCLKH)

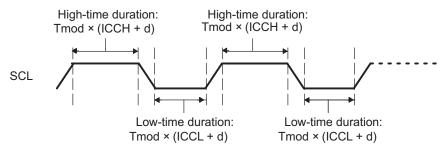

As explained in Section 20.1.4, when the I2C module is a master, the I2C module clock is divided down further to use as the master clock on the SCL pin. As shown in Figure 20-4, the shape of the master clock depends on two divide-down values:

- ICCL in I2CCLKL. For each master clock cycle, ICCL determines the amount of time the signal is low.

- ICCH in I2CCKLH. For each master clock cycle, ICCH determines the amount of time the signal is high.

#### 20.1.5.1 Formula for the Master Clock Period

The master clock period (Tmst) is a multiple of the period of the I2C Module Clock (Tmod):

Master Clock period (Tmst) =  $\frac{[(ICCH + d) + (ICCL + d)]}{I2C Module Clock (Fmod)}$

where d depends on the divide-down value IPSC, as shown in Table 20-1. IPSC is described in the I2CPSC register.

# Table 20-1. Dependency of Delay d on the Divide-DownValue IPSC

| IPSC           | d |

|----------------|---|

| 0              | 7 |

| 1              | 6 |

| Greater than 1 | 5 |

#### 20.2 Configuring Device Pins

The GPIO mux registers must be configured to connect this peripheral to the device pins. To avoid glitches on the pins, the GPyGMUX bits must be configured first (while keeping the corresponding GPyMUX bits at the default of zero), followed by writing the GPyMUX register to the desired value.

Some IO functionality is defined by GPIO register settings independent of this peripheral. For input signals, the GPIO input qualification should be set to asynchronous mode by setting the appropriate GPxQSELn register bits to 11b. The internal pullups can be configured in the GPyPUD register.

See the GPIO chapter for more details on GPIO mux and settings.

#### 20.3 I2C Module Operational Details

This section provides an overview of the I2C bus protocol and how it is implemented.

#### 20.3.1 Input and Output Voltage Levels

One clock pulse is generated by the master device for each data bit transferred. Due to a variety of different technology devices that can be connected to the I2C bus, the levels of logic 0 (low) and logic 1 (high) are not fixed and depend on the associated level of  $V_{DD}$ . For details, see the data manual for your particular device.

#### 20.3.2 Data Validity

The data on SDA must be stable during the high period of the clock (see Figure 20-5). The high or low state of the data line, SDA, should change only when the clock signal on SCL is low.

# SDA \_\_\_\_\_\_STABLE data \_\_\_\_\_STABLE data \_\_\_\_\_STABLE

#### Figure 20-5. Bit Transfer on the I2C bus

#### 20.3.3 Operating Modes

The I2C module has four basic operating modes to support data transfers as a master and as a slave. See Table 20-2 for the names and descriptions of the modes.

If the I2C module is a master, it begins as a master-transmitter and typically transmits an address for a particular slave. When giving data to the slave, the I2C module must remain a master-transmitter. To receive data from a slave, the I2C module must be changed to the master-receiver mode.

If the I2C module is a slave, it begins as a slave-receiver and typically sends acknowledgment when it recognizes its slave address from a master. If the master will be sending data to the I2C module, the module must remain a slave-receiver. If the master has requested data from the I2C module, the module must be changed to the slave-transmitter mode.

| Operating Mode       | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slave-receiver modes | The I2C module is a slave and receives data from a master.                                                                                                                                                                                                                                                                                                                                       |

|                      | All slaves begin in this mode. In this mode, serial data bits received on SDA are shifted in with the clock pulses that are generated by the master. As a slave, the I2C module does not generate the clock signal, but it can hold SCL low while the intervention of the device is required (RSFULL = 1 in I2CSTR) after a byte has been received. See section Section 20.3.7 for more details. |

TEXAS INSTRUMENTS

www.ti.com

| Operating Mode           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Slave-transmitter mode   | The I2C module is a slave and transmits data to a master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                          | This mode can be entered only from the slave-receiver mode; the I2C module must first receive a command from the master. When you are using any of the 7-bit/10-bit addressing formats, the I2C module enters its slave-transmitter mode if the slave address byte is the same as its own address (in I2COAR) and the master has transmitted $R/W = 1$ . As a slave-transmitter, the I2C module then shifts the serial data out on SDA with the clock pulses that are generated by the master. While a slave, the I2C module does not generate the clock signal, but it can hold SCL low while the intervention of the device is required (XSMT = 0 in I2CSTR) after a byte has been transmitted. See section Section 20.3.7 for more details. |

| Master-receiver mode     | The I2C module is a master and receives data from a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                          | This mode can be entered only from the master-transmitter mode; the I2C module must first transmit a command to the slave. When you are using any of the 7-bit/10-bit addressing formats, the I2C module enters its master-receiver mode after transmitting the slave address byte and $R/W = 1$ . Serial data bits on SDA are shifted into the I2C module with the clock pulses generated by the I2C module on SCL. The clock pulses are inhibited and SCL is held low when the intervention of the device is required (RSFULL = 1 in I2CSTR) after a byte has been received.                                                                                                                                                                 |

| Master-transmitter modes | The I2C module is a master and transmits control information and data to a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                          | All masters begin in this mode. In this mode, data assembled in any of the 7-bit/10-bit addressing formats is shifted out on SDA. The bit shifting is synchronized with the clock pulses generated by the I2C module on SCL. The clock pulses are inhibited and SCL is held low when the intervention of the device is required (XSMT = 0 in I2CSTR) after a byte has been transmitted.                                                                                                                                                                                                                                                                                                                                                        |

Table 20-2. Operating Modes of the I2C Module (continued)

To summarize, SCL will be held low in the following conditions:

- When an overrun condition is detected (RSFULL = 1), in Slave-receiver mode.

- When an underflow condition is detected (XSMT = 0), in Slave-transmitter mode.

I2C slave nodes have to accept and provide data when the I2C master node requests it.

- To release SCL in slave-receiver mode, read data from I2CDRR.

- To release SCL in slave-transmitter mode, write data to I2CDXR.

- To force a release without handling the data, reset the module using the I2CMDR.IRS bit.

## Table 20-3. Master-Transmitter/Receiver Bus Activity Defined by the RM, STT, and STP Bits of I2CMDR

| RM | STT | STP | Bus Activity <sup>(1)</sup> | Description                                                                                                                                      |  |  |  |  |

|----|-----|-----|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0  | 0   | 0   | None                        | No activity                                                                                                                                      |  |  |  |  |

| 0  | 0   | 1   | Р                           | STOP condition                                                                                                                                   |  |  |  |  |

| 0  | 1   | 0   | S-A-D(n)D.                  | n)D. START condition, slave address, n data bytes (n = value in I2CCNT)<br>n)D-P START condition, slave address, n data bytes, STOP condition (n |  |  |  |  |

| 0  | 1   | 1   | S-A-D(n)D-P                 | START condition, slave address, n data bytes, STOP condition (n = value in I2CCNT)                                                               |  |  |  |  |

| 1  | 0   | 0   | None                        | No activity                                                                                                                                      |  |  |  |  |

| 1  | 0   | 1   | Р                           | STOP condition                                                                                                                                   |  |  |  |  |

| 1  | 1   | 0   | S-A-D-D-D.                  | Repeat mode transfer: START condition, slave address, continuous data transfers until STOP condition or next START condition                     |  |  |  |  |

| 1  | 1   | 1   | None                        | Reserved bit combination (No activity)                                                                                                           |  |  |  |  |

<sup>(1)</sup> S = START condition; A = Address; D = Data byte; P = STOP condition;

#### 20.3.4 I2C Module START and STOP Conditions

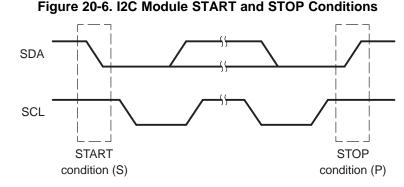

START and STOP conditions can be generated by the I2C module when the module is configured to be a master on the I2C bus. As shown in Figure 20-6:

• The START condition is defined as a high-to-low transition on the SDA line while SCL is high. A master drives this condition to indicate the start of a data transfer.

#### I2C Module Operational Details

• The STOP condition is defined as a low-to-high transition on the SDA line while SCL is high. A master drives this condition to indicate the end of a data transfer.

After a START condition and before a subsequent STOP condition, the I2C bus is considered busy, and the bus busy (BB) bit of I2CSTR is 1. Between a STOP condition and the next START condition, the bus is considered free, and BB is 0.

For the I2C module to start a data transfer with a START condition, the master mode bit (MST) and the START condition bit (STT) in I2CMDR must both be 1. For the I2C module to end a data transfer with a STOP condition, the STOP condition bit (STP) must be set to 1. When the BB bit is set to 1 and the STT bit is set to 1, a repeated START condition is generated. For a description of I2CMDR and its bits (including MST, STT, and STP), see *Registers* Section 20.6.

The I2C peripheral cannot detect a START or STOP condition while it is in reset (IRS = 0). The BB bit will remain in the cleared state (BB = 0) while the I2C peripheral is in reset (IRS = 0). When the I2C peripheral is taken out of reset (IRS set to 1) the BB bit will not correctly reflect the I2C bus status until a START or STOP condition is detected.

Follow these steps before initiating the first data transfer with I2C:

- After taking the I2C peripheral out of reset by setting the IRS bit to 1, wait a period larger than the total time taken for the longest data transfer in the application. By waiting for a period of time after I2C comes out of reset, users can ensure that at least one START or STOP condition will have occurred on the I2C bus and been captured by the BB bit. After this period, the BB bit will correctly reflect the state of the I2C bus.

- 2. Check the BB bit and verify that BB = 0 (bus not busy) before proceeding.

- 3. Begin data transfers.

Not resetting the I2C peripheral in between transfers ensures that the BB bit reflects the actual bus status. If users must reset the I2C peripheral in between transfers, repeat steps 1 through 3 every time the I2C peripheral is taken out of reset.

#### 20.3.5 Serial Data Formats

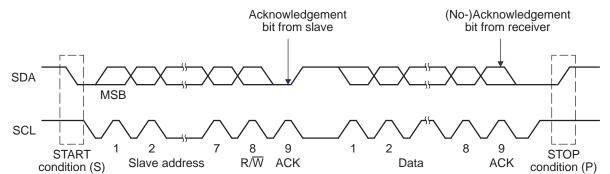

Figure 20-7 shows an example of a data transfer on the I2C bus. The I2C module supports 1 to 8-bit data values. In Figure 20-7, 8-bit data is transferred. Each bit put on the SDA line equates to 1 pulse on the SCL line, and the values are always transferred with the most significant bit (MSB) first. The number of data values that can be transmitted or received is unrestricted. The serial data format used in Figure 20-7 is the 7-bit addressing format. The I2C module supports the formats shown in Figure 20-8 through Figure 20-10 and described in the paragraphs that follow the figures.

**NOTE:** In Figure 20-7 through Figure 20-10, n = the number of data bits (from 1 to 8) specified by the bit count (BC) field of I2CMDR.

#### Figure 20-7. I2C Module Data Transfer (7-Bit Addressing with 8-bit Data Configuration Shown)

#### 20.3.5.1 7-Bit Addressing Format

The 7-bit addressing format is the default format after reset. Disabling expanded address (I2CMDR.XA = 0) and free data format (I2CMDR.FDF = 0) enables 7-bit addressing format.

In this format (see Figure 20-8), the first byte after a START condition (S) consists of a 7-bit slave address followed by a R/W bit. R/W determines the direction of the data:

- R/W = 0: The I2C master writes (transmits) data to the addressed slave. This can be achieved by setting I2CMDR.TRX = 1 (Transmitter mode)

- R/W = 1: The I2C master reads (receives) data from the slave. This can be achieved by setting I2CMDR.TRX = 0 (Receiver mode)

#### Figure 20-8. I2C Module 7-Bit Addressing Format (FDF = 0, XA = 0 in I2CMDR)

| 1 | ← 7 ─ →         | 1   | 1   | • n• | 1   | • n• | 1   | 1 |

|---|-----------------|-----|-----|------|-----|------|-----|---|

| S | x x x x x x x x | R/W | ACK | Data | ACK | Data | ACK | Ρ |

7 bits of slave address

An extra clock cycle dedicated for acknowledgment (ACK) is inserted after each byte. If the ACK bit is inserted by the slave after the first byte from the master, it is followed by n bits of data from the transmitter (master or slave, depending on the R/W bit). n is a number from 1 to 8 determined by the bit count (BC) field of I2CMDR. After the data bits have been transferred, the receiver inserts an ACK bit.

#### 20.3.5.2 10-Bit Addressing Format

The 10-bit addressing format can be enabled by setting expanded address (I2CMDR.XA = 1) and disabling free data format (I2CMDR.FDF = 0).

The 10-bit addressing format (see Figure 20-9) is similar to the 7-bit addressing format, but the master sends the slave address in two separate byte transfers. The first byte consists of 11110b, the two MSBs of the 10-bit slave address, and R/W. The second byte is the remaining 8 bits of the 10-bit slave address. The slave must send acknowledgment after each of the two byte transfers. Once the master has written the second byte to the slave, the master can either write data or use a repeated START condition to change the data direction. For more details about using 10-bit addressing, see the NXP Semiconductors I2C bus specification.

| Figure 20-9. I2C Module 10-Bit Addressing | Format (FDF = 0, XA = 1 in I2CMDR) |

|-------------------------------------------|------------------------------------|

| riguro zo or izo modulo ro Bit Addressing |                                    |

| 1 | 7             | ▶ 1 | 1   | 8                       | 1   | • n  | ▶ 1  1 |

|---|---------------|-----|-----|-------------------------|-----|------|--------|

| S | 1 1 1 1 0 x x | R/W | ACK | x x x x x x x x x       | ACK | Data | ACK P  |

|   | x x = 2 MSBs  |     |     | 8 LSBs of slave address |     |      |        |

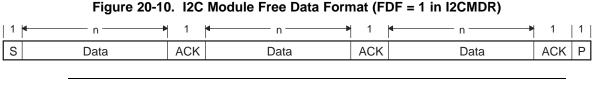

#### 20.3.5.3 Free Data Format

The free data format can be enabled by setting I2CMDR. FDF = 1.

#### I2C Module Operational Details

www.ti.com

In this format (see Figure 20-10), the first byte after a START condition (S) is a data byte. An ACK bit is inserted after each data byte, which can be from 1 to 8 bits, depending on the BC field of I2CMDR. No address or data-direction bit is sent. Therefore, the transmitter and the receiver must both support the free data format, and the direction of the data must be constant throughout the transfer.

**NOTE:** The free data format is not supported in the digital loopback mode (I2CMDR.DLB = 1).

Table 20-4. How the MST and FDF Bits of I2CMDR Affect the Role of the TRX Bit of I2CMDR

| MST | FDF | I2C Module State                                | Function of TRX                                                                                                                                                          |

|-----|-----|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | In slave mode but not free data format mode     | TRX is a don't care. Depending on the command from the master, the I2C module responds as a receiver or a transmitter.                                                   |

| 0   | 1   | In slave mode and free data format mode         | The free data format mode requires that the I2C module remains the<br>transmitter or the receiver throughout the transfer. TRX identifies the role<br>of the I2C module: |

|     |     |                                                 | TRX = 1: The I2C module is a transmitter.<br>TRX = 0: The I2C module is a receiver.                                                                                      |

| 1   | 0   | In master mode but not free data<br>format mode | TRX = 1: The I2C module is a transmitter.<br>TRX = 0: The I2C module is a receiver.                                                                                      |

| 1   | 1   | In master mode and free data format mode        | TRX = 0: The I2C module is a receiver.<br>TRX = 1: The I2C module is a transmitter.                                                                                      |

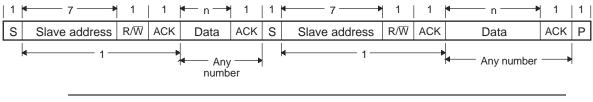

#### 20.3.5.4 Using a Repeated START Condition

I2C master can communicate with multiple slave addresses without having to give up control of the I2C bus by driving a STOP condition. This can be achieved by driving another START condition at the end of each data type. The repeated START condition can be used with the 7-bit addressing, 10-bit addressing, and free data formats. Figure 20-11 shows a repeated START condition in the 7-bit addressing format.

Figure 20-11. Repeated START Condition (in This Case, 7-Bit Addressing Format)

**NOTE:** In Figure 20-11, n = the number of data bits (from 1 to 8) specified by the bit count (BC) field of I2CMDR.

#### 20.3.6 NACK Bit Generation

When the I2C module is a receiver (master or slave), it can acknowledge or ignore bits sent by the transmitter. To ignore any new bits, the I2C module must send a no-acknowledge (NACK) bit during the acknowledge cycle on the bus. Table 20-5 summarizes the various ways you can tell the I2C module to send a NACK bit.

#### Figure 20-14. Pin Diagram Showing the Effects of the Digital Loopback Mode (DLB) Bit

**NOTE:** The free data format (I2CMDR.FDF = 1) is not supported in digital loopback mode.

#### 20.4 Interrupt Requests Generated by the I2C Module

Each I2C module can generate two CPU interrupts.

- 1. Basic I2C interrupt: Possible basic I2C interrupt sources which can trigger this interrupt are described in Section 20.4.1.

- 2. I2C FIFO interrupt: Possible I2C FIFO interrupt sources which can trigger this interrupt are described in Section 20.4.2

#### 20.4.1 Basic I2C Interrupt Requests

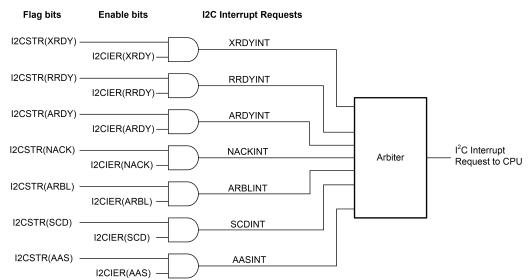

The I2C module generates the interrupt requests described in Table 20-6. As shown in Figure 20-15, all requests are multiplexed through an arbiter to a single I2C interrupt request to the CPU. Each interrupt request has a flag bit in the status register (I2CSTR) and an enable bit in the interrupt enable register (I2CIER). When one of the specified events occurs, its flag bit is set. If the corresponding enable bit is 0, the interrupt request is blocked. If the enable bit is 1, the request is forwarded to the CPU as an I2C interrupt.

The I2C interrupt is one of the maskable interrupts of the CPU. As with any maskable interrupt request, if it is properly enabled in the CPU, the CPU executes the corresponding interrupt service routine (I2CINT1A\_ISR). The I2CINT1A\_ISR for the I2C interrupt can determine the interrupt source by reading the interrupt source register, I2CISRC. Then the I2CINT1A\_ISR can branch to the appropriate subroutine.

After the CPU reads I2CISRC, the following events occur:

- 1. The flag for the source interrupt is cleared in I2CSTR. Exception: The ARDY, RRDY, and XRDY bits in I2CSTR are not cleared when I2CISRC is read. To clear one of these bits, write a 1 to it.

- 2. The arbiter determines which of the remaining interrupt requests has the highest priority, writes the code for that interrupt to I2CISRC, and forwards the interrupt request to the CPU.

| I2C Interrupt Request | Interrupt Source                                                                                                                                                                         |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRDYINT               | Transmit ready condition: The data transmit register (I2CDXR) is ready to accept new data because the previous data has been copied from I2CDXR to the transmit shift register (I2CXSR). |

|                       | As an alternative to using XRDYINT, the CPU can poll the XRDY bit of the status register, I2CSTR. XRDYINT should not be used when in FIFO mode. Use the FIFO interrupts instead.         |

| RRDYINT               | Receive ready condition: The data receive register (I2CDRR) is ready to be read because data has been copied from the receive shift register (I2CRSR) to I2CDRR.                         |

|                       | As an alternative to using RRDYINT, the CPU can poll the RRDY bit of I2CSTR. RRDYINT should not be used when in FIFO mode. Use the FIFO interrupts instead.                              |

| ARDYINT               | Register-access ready condition: The I2C module registers are ready to be accessed because the previously programmed address, data, and command values have been used.                   |

|                       | The specific events that generate ARDYINT are the same events that set the ARDY bit of I2CSTR.                                                                                           |

|                       | As an alternative to using ARDYINT, the CPU can poll the ARDY bit.                                                                                                                       |

| NACKINT               | No-acknowledgment condition: The I2C module is configured as a master-transmitter and did not received acknowledgment from the slave-receiver.                                           |

|                       | As an alternative to using NACKINT, the CPU can poll the NACK bit of I2CSTR.                                                                                                             |

| ARBLINT               | Arbitration-lost condition: The I2C module has lost an arbitration contest with another master-transmitter.                                                                              |

|                       | As an alternative to using ARBLINT, the CPU can poll the ARBL bit of I2CSTR.                                                                                                             |

| SCDINT                | Stop condition detected: A STOP condition was detected on the I2C bus.                                                                                                                   |

|                       | As an alternative to using SCDINT, the CPU can poll the SCD bit of the status register, I2CSTR.                                                                                          |

| AASINT                | Addressed as slave condition: The I2C has been addressed as a slave device by another master on the I2C bus.                                                                             |

|                       | As an alternative to using AASINT, the CPU can poll the AAS bit of the status register, I2CSTR.                                                                                          |

#### Table 20-6. Descriptions of the Basic I2C Interrupt Requests

#### Figure 20-15. Enable Paths of the I2C Interrupt Requests

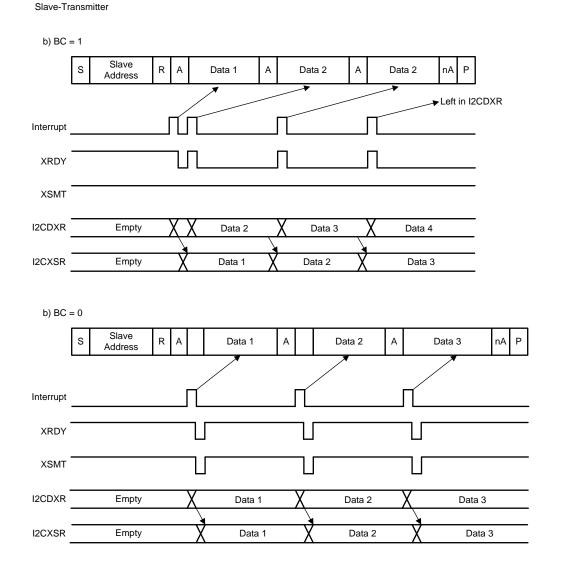

The I2C module has a backwards compatibility bit (BC) in the I2CEMDR register. The timing diagram in Figure 20-16 demonstrates the effect the backwards compatibility bit has on I2C module registers and interrupts when configured as a slave-transmitter.

#### Figure 20-16. Backwards Compatibility Mode Bit, Slave Transmitter

#### 20.4.2 I2C FIFO Interrupts

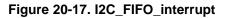

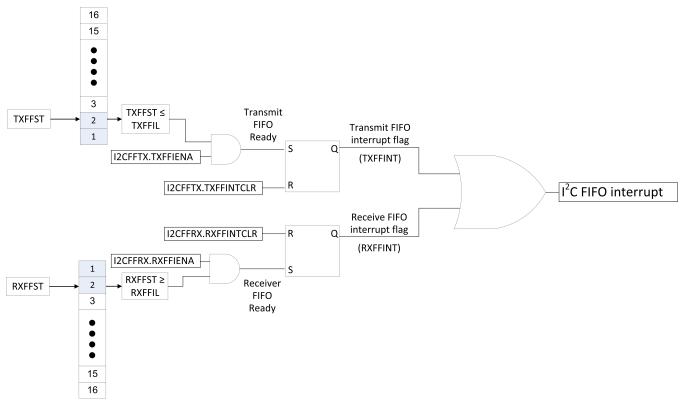

In addition to the seven basic I2C interrupts, the transmit and receive FIFOs each contain the ability to generate an interrupt (I2CINT2A). The transmit FIFO can be configured to generate an interrupt after transmitting a defined number of bytes, up to 16. The receive FIFO can be configured to generate an interrupt after receiving a defined number of bytes, up to 16. These two interrupt sources are ORed together into a single maskable CPU interrupt. Figure 20-17 shows the structure of I2C FIFO interrupt. The interrupt service routine can then read the FIFO interrupt status flags to determine from which source the interrupt came. See the I2C transmit FIFO register (I2CFFTX) and the I2C receive FIFO register (I2CFFRX) descriptions.

#### Resetting or Disabling the I2C Module

#### 20.5 Resetting or Disabling the I2C Module

You can reset or disable the I2C module in two ways:

- Write 0 to the I2C reset bit (IRS) in the I2C mode register (I2CMDR). All status bits (in I2CSTR) are forced to their default values, and the I2C module remains disabled until IRS is changed to 1. The SDA and SCL pins are in the high-impedance state.

- Initiate a device reset by driving the XRS pin low. The entire device is reset and is held in the reset state until you drive the pin high. When the XRS pin is released, all I2C module registers are reset to their default values. The IRS bit is forced to 0, which resets the I2C module. The I2C module stays in the reset state until you write 1 to IRS.

The IRS must be 0 while you configure or reconfigure the I2C module. Forcing IRS to 0 can be used to save power and to clear error conditions.

#### 20.6.2 I2C\_REGS Registers

Table 20-8 lists the I2C\_REGS registers. All register offset addresses not listed in Table 20-8 should be considered as reserved locations and the register contents should not be modified.

| Offset | Acronym | Register Name               | Write Protection | Section |

|--------|---------|-----------------------------|------------------|---------|

| 0h     | I2COAR  | I2C Own address             |                  | Go      |

| 1h     | I2CIER  | I2C Interrupt Enable        |                  | Go      |

| 2h     | I2CSTR  | I2C Status                  |                  | Go      |

| 3h     | I2CCLKL | I2C Clock low-time divider  |                  | Go      |

| 4h     | I2CCLKH | I2C Clock high-time divider |                  | Go      |

| 5h     | I2CCNT  | I2C Data count              |                  | Go      |

| 6h     | I2CDRR  | I2C Data receive            |                  | Go      |

| 7h     | I2CSAR  | I2C Slave address           |                  | Go      |

| 8h     | I2CDXR  | I2C Data Transmit           |                  | Go      |

| 9h     | I2CMDR  | I2C Mode                    |                  | Go      |

| Ah     | I2CISRC | I2C Interrupt Source        |                  | Go      |

| Bh     | I2CEMDR | I2C Extended Mode           |                  | Go      |

| Ch     | I2CPSC  | I2C Prescaler               |                  | Go      |

| 20h    | I2CFFTX | I2C FIFO Transmit           |                  | Go      |

| 21h    | I2CFFRX | I2C FIFO Receive            |                  | Go      |

#### Table 20-8. I2C\_REGS Registers

Complex bit access types are encoded to fit into small table cells. Table 20-9 shows the codes that are used for access types in this section.

| Access Type      | Code      | Description                                                                                                                                                                                                                                                                                                  |

|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Type        |           |                                                                                                                                                                                                                                                                                                              |

| R                | R         | Read                                                                                                                                                                                                                                                                                                         |

| R-0              | R<br>-0   | Read<br>Returns 0s                                                                                                                                                                                                                                                                                           |

| Write Type       |           |                                                                                                                                                                                                                                                                                                              |

| W                | W         | Write                                                                                                                                                                                                                                                                                                        |

| W1C              | W<br>1C   | Write<br>1 to clear                                                                                                                                                                                                                                                                                          |

| W1S              | W<br>1S   | Write<br>1 to set                                                                                                                                                                                                                                                                                            |

| Reset or Default | Value     |                                                                                                                                                                                                                                                                                                              |

| -n               |           | Value after reset or the default value                                                                                                                                                                                                                                                                       |

| Register Array \ | /ariables |                                                                                                                                                                                                                                                                                                              |

| i,j,k,l,m,n      |           | When these variables are used in<br>a register name, an offset, or an<br>address, they refer to the value of<br>a register array where the register<br>is part of a group of repeating<br>registers. The register groups form<br>a hierarchical structure and the<br>array is represented with a<br>formula. |

| У                |           | When this variable is used in a register name, an offset, or an address it refers to the value of a register array.                                                                                                                                                                                          |

#### Table 20-9. I2C\_REGS Access Type Codes

#### 20.6.2.1 I2COAR Register (Offset = 0h) [reset = 0h]

I2COAR is shown in Figure 20-18 and described in Table 20-10.

Return to the Summary Table.

The I2C own address register (I2COAR) is a 16-bit register. The I2C module uses this register to specify its own slave address, which distinguishes it from other slaves connected to the I2C-bus. If the 7-bit addressing mode is selected (XA = 0 in I2CMDR), only bits 6-0 are used write 0s to bits 9-7.

| Figure   | 20-18. | <b>I2COAR</b> | Register |

|----------|--------|---------------|----------|

| i igui o | 20 101 | 1200/00       | regiotor |

|        |          |    | •  |    | •  |   |      |

|--------|----------|----|----|----|----|---|------|

| 15     | 14       | 13 | 12 | 11 | 10 | 9 | 8    |

|        | RESERVED |    |    |    |    |   |      |

|        | R-0h     |    |    |    |    |   | /-0h |

| 7      | 6        | 5  | 4  | 3  | 2  | 1 | 0    |

| OAR    |          |    |    |    |    |   |      |

| R/W-0h |          |    |    |    |    |   |      |

#### Table 20-10. I2COAR Register Field Descriptions

| Bit   | Field    | Туре | Reset | Description                                                                               |

|-------|----------|------|-------|-------------------------------------------------------------------------------------------|

| 15-10 | RESERVED | R    | 0h    | Reserved                                                                                  |

| 9-0   | OAR      | R/W  | 0h    | In 7-bit addressing mode (XA = 0 in I2CMDR):                                              |

|       |          |      |       | 00h-7Fh Bits 6-0 provide the 7-bit slave address of the I2C module. Write 0s to bits 9-7. |

|       |          |      |       | In 10-bit addressing mode (XA = 1 in I2CMDR):                                             |

|       |          |      |       | 000h-3FFh Bits 9-0 provide the 10-bit slave address of the I2C module.                    |

|       |          |      |       | Reset type: SYSRSn                                                                        |

#### 20.6.2.2 I2CIER Register (Offset = 1h) [reset = 0h]

I2CIER is shown in Figure 20-19 and described in Table 20-11.

Return to the Summary Table.

I2CIER is used by the CPU to individually enable or disable I2C interrupt requests.

#### Figure 20-19. I2CIER Register

|          |          |        | •      | -      |        |        |        |

|----------|----------|--------|--------|--------|--------|--------|--------|

| 15       | 14       | 13     | 12     | 11     | 10     | 9      | 8      |

|          | RESERVED |        |        |        |        |        |        |

|          |          |        | R-     | •0h    |        |        |        |

| 7        | 6        | 5      | 4      | 3      | 2      | 1      | 0      |

| RESERVED | AAS      | SCD    | XRDY   | RRDY   | ARDY   | NACK   | ARBL   |

| R-0h     | R/W-0h   | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h | R/W-0h |

|          |          |        |        |        |        |        |        |

#### Table 20-11. I2CIER Register Field Descriptions

| Bit  | Field    | Туре | Reset | Description                                                                                                                                                                                          |

|------|----------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-7 | RESERVED | R    | 0h    | Reserved                                                                                                                                                                                             |

| 6    | AAS      | R/W  | Oh    | Addressed as slave interrupt enable<br>Reset type: SYSRSn<br>Oh (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled                                                           |

| 5    | SCD      | R/W  | Oh    | Stop condition detected interrupt enable<br>Reset type: SYSRSn<br>Oh (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled                                                      |

| 4    | XRDY     | R/W  | Oh    | Transmit-data-ready interrupt enable bit.<br>This bit should not be set when using FIFO mode.<br>Reset type: SYSRSn<br>Oh (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled |

| 3    | RRDY     | R/W  | Oh    | Receive-data-ready interrupt enable bit.<br>This bit should not be set when using FIFO mode.<br>Reset type: SYSRSn<br>0h (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled  |

| 2    | ARDY     | R/W  | Oh    | Register-access-ready interrupt enable<br>Reset type: SYSRSn<br>Oh (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled                                                        |

| 1    | NACK     | R/W  | Oh    | No-acknowledgment interrupt enable<br>Reset type: SYSRSn<br>Oh (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled                                                            |

| 0    | ARBL     | R/W  | Oh    | Arbitration-lost interrupt enable<br>Reset type: SYSRSn<br>0h (R/W) = Interrupt request disabled<br>1h (R/W) = Interrupt request enabled                                                             |

#### 20.6.2.3 I2CSTR Register (Offset = 2h) [reset = 410h]

I2CSTR is shown in Figure 20-20 and described in Table 20-12.

Return to the Summary Table.

The I2C status register (I2CSTR) is a 16-bit register used to determine which interrupt has occurred and to read status information.

|          |                               | Figure 20-2                          | U. 12031 K Reg                                                                                                                                                                              | Jister                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                       |                                                                                         |

|----------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 14       | 13                            | 12                                   | 11                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                        | 9                                                                                                                                                                                                                                                                                                                     | 8                                                                                       |

| SDIR     | NACKSNT                       | BB                                   | RSFULL                                                                                                                                                                                      | XSMT                                                                                                                                                                                                                                                      | AAS                                                                                                                                                                                                                                                                                                                   | AD0                                                                                     |

| R/W1C-0h | R/W1C-0h                      | R-0h                                 | R-0h                                                                                                                                                                                        | R-1h                                                                                                                                                                                                                                                      | R-0h                                                                                                                                                                                                                                                                                                                  | R-0h                                                                                    |

| 6        | 5                             | 4                                    | 3                                                                                                                                                                                           | 2                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                     | 0                                                                                       |

| RVED     | SCD                           | XRDY                                 | RRDY                                                                                                                                                                                        | ARDY                                                                                                                                                                                                                                                      | NACK                                                                                                                                                                                                                                                                                                                  | ARBL                                                                                    |

| /-0h     | R/W1C-0h                      | R-1h                                 | R/W1C-0h                                                                                                                                                                                    | R/W1C-0h                                                                                                                                                                                                                                                  | R/W1C-0h                                                                                                                                                                                                                                                                                                              | R/W1C-0h                                                                                |

|          | SDIR<br>R/W1C-0h<br>6<br>RVED | SDIRNACKSNTR/W1C-0hR/W1C-0h65RVEDSCD | 14         13         12           SDIR         NACKSNT         BB           R/W1C-0h         R/W1C-0h         R-0h           6         5         4           RVED         SCD         XRDY | 14         13         12         11           SDIR         NACKSNT         BB         RSFULL           R/W1C-0h         R/W1C-0h         R-0h         R-0h           6         5         4         3           RVED         SCD         XRDY         RRDY | 14         13         12         11         10           SDIR         NACKSNT         BB         RSFULL         XSMT           R/W1C-0h         R/W1C-0h         R-0h         R-0h         R-1h           6         5         4         3         2           RVED         SCD         XRDY         RRDY         ARDY | SDIRNACKSNTBBRSFULLXSMTAASR/W1C-0hR/W1C-0hR-0hR-0hR-1hR-0h654321RVEDSCDXRDYRRDYARDYNACK |

#### Figure 20-20. I2CSTR Register

#### Table 20-12. I2CSTR Register Field Descriptions

| Bit | Field    | Туре  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | RESERVED | R     | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 14  | SDIR     | R/W1C | Oh    | <ul> <li>Slave direction bit</li> <li>Reset type: SYSRSn</li> <li>Oh (R/W) = I2C is not addressed as a slave transmitter. SDIR is cleared by one of the following events:</li> <li>It is manually cleared. To clear this bit, write a 1 to it.</li> <li>Digital loopback mode is enabled.</li> <li>A START or STOP condition occurs on the I2C bus.</li> <li>1h (R/W) = I2C is addressed as a slave transmitter.</li> </ul>                                                                                                                                                                                                                               |

| 13  | NACKSNT  | R/W1C | Oh    | <ul> <li>NACK sent bit.</li> <li>This bit is used when the I2C module is in the receiver mode. One instance in which NACKSNT is affected is when the NACK mode is used (see the description for NACKMOD in Reset type: SYSRSn</li> <li>Oh (R/W) = NACK not sent. NACKSNT bit is cleared by any one of the following events: <ul> <li>It is manually cleared. To clear this bit, write a 1 to it.</li> <li>The I2C module is reset (either when 0 is written to the IRS bit of I2CMDR or when the whole device is reset).</li> <li>Ih (R/W) = NACK sent: A no-acknowledge bit was sent during the acknowledge cycle on the I2C-bus.</li> </ul> </li> </ul> |

| 12  | BB       | R     | Oh    | <ul> <li>Bus busy bit.</li> <li>BB indicates whether the I2C-bus is busy or is free for another data transfer. See the paragraph following the table for more information Reset type: SYSRSn</li> <li>Oh (R/W) = Bus free. BB is cleared by any one of the following events:</li> <li>The I2C module receives or transmits a STOP bit (bus free).</li> <li>The I2C module is reset.</li> <li>1h (R/W) = Bus busy: The I2C module has received or transmitted a START bit on the bus.</li> </ul>                                                                                                                                                           |

| Bit | Field    | Туре  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | RSFULL   | R     | 0h    | Receive shift register full bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |       |       | RSFULL indicates an overrun condition during reception. Overrun occurs when new data is received into the shift register (I2CRSR) and the old data has not been read from the receive register (I2CDRR). As new bits arrive from the SDA pin, they overwrite the bits in I2CRSR. The new data will not be copied to ICDRR until the previous data is read.<br>Reset type: SYSRSn<br>Oh (R/W) = No overrun detected. RSFULL is cleared by any one of the following events:<br>- I2CDRR is read is read by the CPU. Emulator reads of the I2CDRR do not affect this bit.<br>- The I2C module is reset.<br>1h (R/W) = Overrun detected                            |

| 10  | XSMT     | R     | 1h    | Transmit shift register empty bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |       |       | XSMT = 0 indicates that the transmitter has experienced underflow.<br>Underflow occurs when the transmit shift register (I2CXSR) is empty<br>but the data transmit register (I2CDXR) has not been loaded since<br>the last I2CDXR-to-I2CXSR transfer. The next I2CDXR-to-I2CXSR<br>transfer will not occur until new data is in I2CDXR. If new data is not<br>transferred in time, the previous data may be re-transmitted on the<br>SDA pin.                                                                                                                                                                                                                  |

|     |          |       |       | Reset type: SYSRSn<br>0h (R/W) = Underflow detected (empty)<br>1h (R/W) = No underflow detected (not empty). XSMT is set by one<br>of the following events:<br>- Data is written to I2CDXR.<br>- The I2C module is reset                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9   | AAS      | R     | Oh    | Addressed-as-slave bit<br>Reset type: SYSRSn<br>0h (R/W) = In the 7-bit addressing mode, the AAS bit is cleared<br>when receiving a NACK, a STOP condition, or a repeated START<br>condition. In the 10-bit addressing mode, the AAS bit is cleared<br>when receiving a NACK, a STOP condition, or by a slave address<br>different from the I2C peripheral's own slave address.<br>1h (R/W) = The I2C module has recognized its own slave address<br>or an address of all zeros (general call).                                                                                                                                                                |

| 8   | AD0      | R     | Oh    | Address 0 bits<br>Reset type: SYSRSn<br>0h (R/W) = AD0 has been cleared by a START or STOP condition.<br>1h (R/W) = An address of all zeros (general call) is detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7-6 | RESERVED | R/W   | 0h    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5   | SCD      | R/W1C | 0h    | Stop condition detected bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |          |       |       | <ul> <li>SCD is set when the I2C sends or receives a STOP condition. The I2C module delays clearing of the I2CMDR[STP] bit until the SCD bit is set.</li> <li>Reset type: SYSRSn</li> <li>Oh (R/W) = STOP condition not detected since SCD was last cleared. SCD is cleared by any one of the following events:</li> <li>I2CISRC is read by the CPU when it contains the value 110b (stop condition detected). Emulator reads of the I2CISRC do not affect this bit.</li> <li>SCD is manually cleared. To clear this bit, write a 1 to it.</li> <li>The I2C module is reset.</li> <li>1h (R/W) = A STOP condition has been detected on the I2C bus.</li> </ul> |

| Table 20-12. | I2CSTR | Register | Field | Descriptions | (continued) |

|--------------|--------|----------|-------|--------------|-------------|

|--------------|--------|----------|-------|--------------|-------------|

| Bit | Field | Туре  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | XRDY  | R     | 1h    | Transmit-data-ready interrupt flag bit.<br>When not in FIFO mode, XRDY indicates that the data transmit<br>register (I2CDXR) is ready to accept new data because the previous<br>data has been copied from I2CDXR to the transmit shift register<br>(I2CXSR). The CPU can poll XRDY or use the XRDY interrupt<br>request When in FIFO mode, use TXFFINT instead.<br>Reset type: SYSRSn<br>0h (R/W) = I2CDXR not ready. XRDY is cleared when data is<br>written to I2CDXR.<br>1h (R/W) = I2CDXR ready: Data has been copied from I2CDXR to<br>I2CXSR.<br>XRDY is also forced to 1 when the I2C module is reset.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3   | RRDY  | R/W1C | Oh    | Receive-data-ready interrupt flag bit.<br>When not in FIFO mode, RRDY indicates that the data receive<br>register (I2CDRR) is ready to be read because data has been copied<br>from the receive shift register (I2CRSR) to I2CDRR. The CPU can<br>poll RRDY or use the RRDY interrupt request When in FIFO mode,<br>use RXFFINT instead.<br>Reset type: SYSRSn<br>0h (R/W) = I2CDRR not ready. RRDY is cleared by any one of the<br>following events:<br>- I2CDRR is read by the CPU. Emulator reads of the I2CDRR do<br>not affect this bit.<br>- RRDY is manually cleared. To clear this bit, write a 1 to it.<br>- The I2C module is reset.<br>1h (R/W) = I2CDRR ready: Data has been copied from I2CRSR to<br>I2CDRR.                                                                                                                                                                                                                                                                                                                     |

| 2   | ARDY  | R/W1C | Oh    | Register-access-ready interrupt flag bit (only applicable when the I2C module is in the master mode).<br>ARDY indicates that the I2C module registers are ready to be accessed because the previously programmed address, data, and command values have been used. The CPU can poll ARDY or use the ARDY interrupt request.<br>Reset type: SYSRSn<br>0h (R/W) = The registers are not ready to be accessed. ARDY is cleared by any one of the following events:<br>- The I2C module starts using the current register contents.<br>- ARDY is manually cleared. To clear this bit, write a 1 to it.<br>- The I2C module is reset.<br>1h (R/W) = The registers are ready to be accessed.<br>In the nonrepeat mode (RM = 0 in I2CMDR): If STP = 0 in I2CMDR, the ARDY bit is set when the internal data counter counts down to 0. If STP = 1, ARDY is not affected (instead, the I2C module generates a STOP condition when the counter reaches 0).<br>In the repeat mode (RM = 1): ARDY is set at the end of each byte transmitted from I2CDXR. |

#### Table 20-12. I2CSTR Register Field Descriptions (continued)

| Bit | Field | Туре  | Reset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |