Page

# Enhanced Pulse Width Modulator (ePWM)

The enhanced pulse width modulator (ePWM) peripheral is a key element in controlling many of the power electronic systems found in both commercial and industrial equipment. These systems include digital motor control, switch mode power supply control, uninterruptible power supplies (UPS), and other forms of power conversion. The ePWM peripheral can also perform a digital to analog (DAC) function, where the duty cycle is equivalent to a DAC analog value; it is sometimes referred to as a power DAC.

This chapter is applicable for ePWM type 4 with added register protection capability. See the *TMS320x28xx*, *28xxx DSP Peripheral Reference Guide* for a list of all devices with an ePWM module of the same type, to determine the differences between the types, and for a list of device-specific differences within a type.

Further information can be found in the following document(s):

Flexible PWMs Enable Multi-Axis Drives, Multi-Level Inverters

#### Topic

15.1 Configuring Device Pins ..... 1869 15.2 15.3 15.4 15.5 15.6 15.7 Dead-Band Generator (DB) Submodule ..... 1902 15.8 PWM Chopper (PC) Submodule ..... 1908 15.9 Trip-Zone (TZ) Submodule ..... 1912 15.10 Event-Trigger (ET) Submodule ..... 1917 15.11 Digital Compare (DC) Submodule ..... 1923 15.13 Applications to Power Topologies ..... 1933 15.14 High-Resolution Pulse Width Modulator (HRPWM) ...... 15.15 ePWM Registers ...... 1978

TEXAS INSTRUMENTS

Introduction

# 15.1 Introduction

This chapter includes an overview and information about each submodule:

- Time-Base Submodule

- Counter Compare Submodule

- Action Qualifier Submodule

- Dead-Band Generator Submodule

- PWM Chopper (PC) Submodule

- Trip Zone Submodule

- Event Trigger Submodule

- Digital Compare Submodule

The ePWM Type 4 is functionally compatible to Type 2 (a Type 3 does not exist). Type 4 has the following enhancements in addition to the Type 2 features:

# Register Address Map

Additional registers are required for new features on ePWM Type 4. The ePWM register address space has been remapped for better alignment and easy usage.

# Delayed Trip Functionality

Changes have been added to achieve deadband insertion capabilities to support, for example, delayed trip functionality needed for peak current mode control type application scenarios. This has been accomplished by allowing comparator events to go into the Action Qualifier as a trigger event (Events T1 and T2). If comparator T1 / T2 events are used to edit the PWM, changes to the PWM waveform will not take place immediately. Instead, they will synchronize to the next TBCLK.

# • Dead-Band Generator Submodule Enhancements

Shadowing of the DBCTL register to allow dynamic configuration changes.

# One Shot and Global Load of Registers

The ePWM Type 4 allows one shot and global load capability from shadow to active registers to avoid partial loads in, for example, multi-phase applications. It also allows a programmable prescale of shadow to active load events. ePWM Type 4 Global Load can simplify ePWM software by removing interrupts and ensuring that all registers are loaded at the same time.

# Trip Zone Submodule Enhancements

Independent flags have been added to reflect the trip status for each of the TZ sources. Changes have been made to the trip zone submodule to support certain power converter switching techniques like valley switching.

## Digital Compare Submodule Enhancements

Blanking window filter register width has been increased from 8 to 16 bits. DCCAP functionality has been enhanced to provide more programmability.

# PWM SYNC Related Enhancements

The ePWM Type 4 allows PWM SYNCOUT generation based on CMPC and CMPD events. These events can also be used for PWMSYNC pulse selection.

The ePWM Type 2 is fully compatible to Type 1. Type 2 has the following enhancements in addition to the Type 1 features:

# High Resolution Dead-Band Capability

High resolution capability is added to dead-band RED and FED in half-cycle clocking mode.

# Dead-Band Generator Submodule Enhancements

The ePWM Type 2 has features to enable both RED and FED on either PWM outputs. Provides increased dead band with 14-bit counters and dead-band / dead-band high-resolution registers are shadowed

# High Resolution Extension available on ePWMxB outputs

Provides the ability to enable high-resolution period and duty cycle control on ePWMxB outputs. This is discussed in more detail in Section 15.14.

## Counter Compare Submodule Enhancements

The ePWM Type 2 allows Interrupts and SOC events to be generated by additional counter compares CMPC and CMPD.

# Event Trigger Submodule Enhancements

Prescaling logic to issue interrupt requests and ADC start of conversion expanded up to every 15 events. It allows software initialization of event counters on SYNC event.

## Digital Compare Submodule Enhancements

Digital Compare Trip Select logic [DCTRIPSEL] has up to 12 external trip sources selected by the Input X-BAR logic in addition to an ability to OR all of them (up to 14 [external and internal sources]) to create the respective DCxEVTs.

# • Simultaneous Writes to TBPRD and CMPx Registers

This feature allows writes to TBPRD, CMPA:CMPAHR, CMPB:CMPBHR, CMPC and CMPD of any ePWM module to be tied to any other ePWM module, and also allows all ePWM modules to be tied to a particular ePWM module if desired.

# Shadow to Active Load on SYNC of TBPRD and CMP Registers

This feature supports simultaneous writes of TBPRD and CMPA/B/C/D registers.

An effective PWM peripheral must be able to generate complex pulse width waveforms with minimal CPU overhead or intervention. It must be highly programmable and very flexible while being easy to understand and use. The ePWM unit described here addresses these requirements by allocating all needed timing and control resources on a per PWM channel basis. Cross coupling or sharing of resources has been avoided; instead, the ePWM is built up from smaller single channel submodules with separate resources that can operate together as required to form a system. This modular approach results in an orthogonal architecture and provides a more transparent view of the peripheral structure, helping users to understand its operation quickly.

In this document, the letter x within a signal or submodule name is used to indicate a generic ePWM instance on a device. For example, output signals EPWMxA and EPWMxB refer to the output signals from the ePWMx instance. Thus, EPWM1A and EPWM1B belong to ePWM1 and likewise EPWM4A and EPWM4B belong to ePWM4.

## Type0 to Type1 Enhancements

## Increased Dead-Band Resolution

Dead-band clocking has been enhanced to allow half-cycle clocking to double resolution.

## • Enhanced Interrupt and SOC Generation

Interrupts and ADC start-of-conversion can now be generated on both the TBCTR == zero and TBCTR == period events. This feature enables dual edge PWM control. Additionally, the ADC start-of-conversion can be generated from an event defined in the digital compare submodule.

## • High Resolution Period Capability

Provides the ability to enable high-resolution period. This is discussed in more detail in the devicespecific *High-Resolution Pulse Width Modulator (HRPWM)* document..

## • Digital Compare Submodule

The digital compare submodule enhances the event triggering and trip zone submodules by providing filtering, blanking and improved trip functionality to digital compare signals. Such features are essential for peak current mode control and for support of analog comparators.

**NOTE:** The name of the sync signal that goes to the CMPSS and GPDAC has been updated from PWMSYNC to EPWMSYNCPER (SYNCPER/PWMSYNCPER/EPWMxSYNCPER) to avoid confusion with the other EPWM sync signals EPWMSYNCI and EPWMSYNCO. For a description of what these signals are, see Table 15-2.

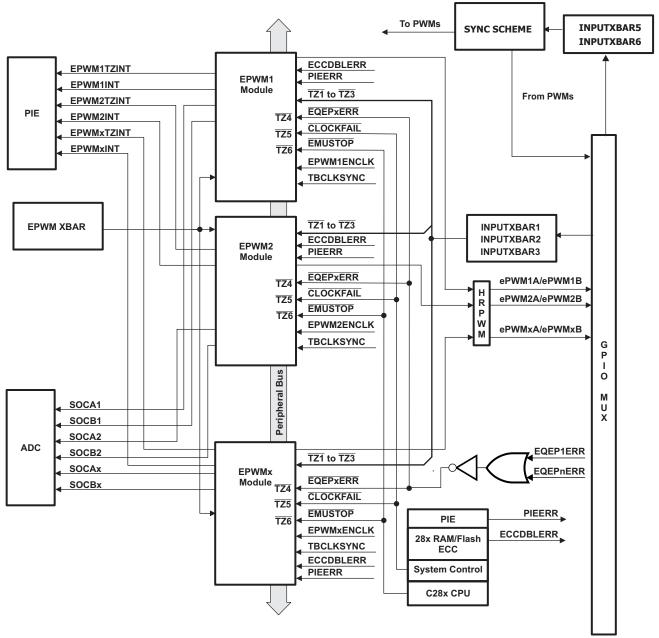

# 15.1.1 Submodule Overview

The ePWM module represents one complete PWM channel composed of two PWM outputs: EPWMxA and EPWMxB. Multiple ePWM modules are instanced within a device as shown in Figure 15-1. Each ePWM instance is identical with one exception. Some instances include a hardware extension that allows more precise control of the PWM outputs. This extension is the high-resolution pulse width modulator (HRPWM) and is described in Section 15.14. See the device-specific data manual to determine which ePWM instances include this feature. Each ePWM module is indicated by a numerical value starting with 1. For example ePWM1 is the first instance and ePWM3 is the third instance in the system and ePWMx indicates any instance.

The ePWM modules are chained together via a clock synchronization scheme that allows them to operate as a single system when required. Additionally, this synchronization scheme can be extended to the capture peripheral submodules (eCAP). The number of submodules is device-dependent and based on target application needs. Submodules can also operate standalone.

Each ePWM module supports the following features:

- Dedicated 16-bit time-base counter with period and frequency control

- Two PWM outputs (EPWMxA and EPWMxB) that can be used in the following configurations:

- Two independent PWM outputs with single-edge operation

- Two independent PWM outputs with dual-edge symmetric operation

- One independent PWM output with dual-edge asymmetric operation

- Asynchronous override control of PWM signals through software.

- Programmable phase-control support for lag or lead operation relative to other ePWM modules.

- Hardware-locked (synchronized) phase relationship on a cycle-by-cycle basis.

- Dead-band generation with independent rising and falling edge delay control.

- Programmable trip zone allocation of both cycle-by-cycle trip and one-shot trip on fault conditions.

- A trip condition can force either high, low, or high-impedance state logic levels at PWM outputs.

- All events can trigger both CPU interrupts and ADC start of conversion (SOC)

- Programmable event prescaling minimizes CPU overhead on interrupts.

- PWM chopping by high-frequency carrier signal, useful for pulse transformer gate drives.

Each ePWM module is connected to the input/output signals shown in Figure 15-1. The signals are described in detail in subsequent sections.

Copyright © 2017, Texas Instruments Incorporated

A This signal exists only on devices with an eQEP submodule.

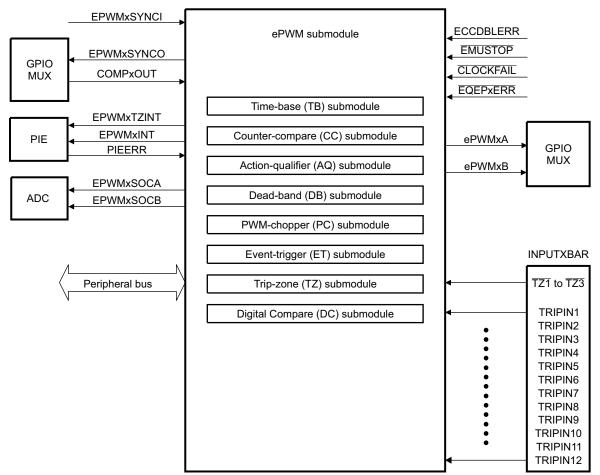

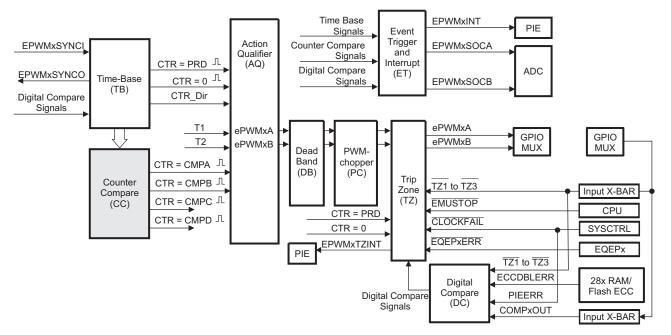

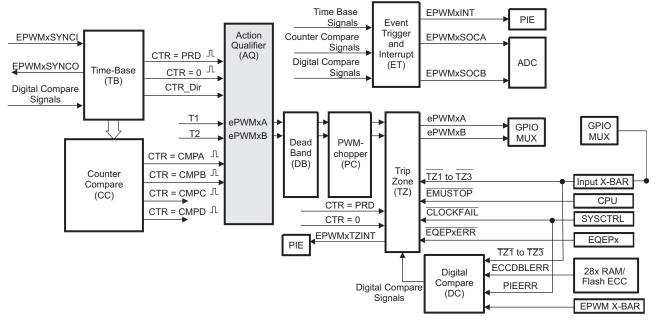

The order in which the ePWM modules are connected may differ from what is shown in Figure 15-1. See Section 15.4.3.3 for the synchronization scheme for a particular device. Each ePWM module consists of eight submodules and is connected within a system via the signals shown in Figure 15-2.

Figure 15-2. Submodules and Signal Connections for an ePWM Module

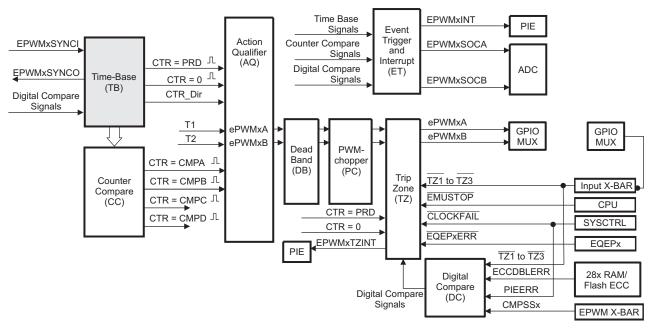

Figure 15-3 shows more internal details of a single ePWM module. The main signals used by the ePWM module are:

• PWM output signals (EPWMxA and EPWMxB).

The PWM output signals are made available external to the device through the GPIO peripheral described in the *System Control and Interrupts* chapter for your device.

Trip-zone signals (TZ1 to TZ6).

These input signals alert the ePWM module of fault conditions external to the ePWM module. Each submodule on a device can be configured to either use or ignore any of the trip-zone signals. The TZ1 to TZ3 trip-zone signals can be configured as asynchronous inputs through the GPIO peripheral using the Input X-BAR logic, refer to . TZ4 is connected to an inverted EQEPx error signal (EQEPxERR), which can be generated from any one of the EQEP submodule (for those devices with an EQEP module). TZ5 is connected to the system clock fail logic, and TZ6 is connected to the EMUSTOP output from the CPU. This allows you to configure a trip action when the clock fails or the CPU halts.

# • Time-base synchronization input (EPWMxSYNCI), output (EPWMxSYNCO) and peripheral (EPWMxSYNCPER) signals.

The synchronization signals daisy chain the ePWM module together. Each module can be configured via INPUTXBAR6 to either use or ignore its synchronization input. The clock synchronization input and output signal are brought out to pins only for ePWM1 (ePWM module #1). The ePWM module are separate into groups of three for syncing purposes. An external sync signal (EXTSYNCIN1 or EXTSYNCIN2) may be used to issue a sync signal to the first ePWM module in each chain. These same module can also send their EPWMxSYNCOUT signal to a GPIO. For more information, see Section 15.4.3.3.

Each ePWM module also generates another PWMSYNC signal called EPWMxSYNCPER.

EPWMxSYNCPER goes to the GPDAC and CMPSS for synchronization purposes. It is configured using the HRPCTL register but has no relation with the HRPWM. For more information on how EPWMxSYNCPER is used by the GPDAC and CMPSS, see their respective chapters.

# • ADC start-of-conversion signals (EPWMxSOCA and EPWMxSOCB).

Each ePWM module has two ADC start of conversion signals. Any ePWM module can trigger a start of conversion. Whichever event triggers the start of conversion is configured in the event-trigger submodule of the ePWM.

# • Comparator output signals (COMPxOUT).

Output signals from the comparator module can be fed through the Input X-BAR to one or all of the 12 trip inputs [TRIPIN1 - TRIPIN12] and in conjunction with the trip zone signals can generate digital compare events.

# • Peripheral Bus

The peripheral bus is 32-bits wide and allows both 16-bit and 32-bit writes to the ePWM register file.

Time-Base (TB) Submodule

#### www.ti.com

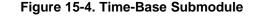

# 15.4 Time-Base (TB) Submodule

Each ePWM module has its own time-base submodule that determines all of the event timing for the ePWM module. Built-in synchronization logic allows the time-base of multiple ePWM modules to work together as a single system. Figure 15-4 illustrates the time-base module's place within the ePWM.

## 15.4.1 Purpose of the Time-Base Submodule

You can configure the time-base submodule for the following:

- Specify the ePWM time-base counter (TBCTR) frequency or period to control how often events occur.

- Manage time-base synchronization with other ePWM modules.

- · Maintain a phase relationship with other ePWM modules.

- Set the time-base counter to count-up, count-down, or count-up-and-down mode.

- Generate the following events:

- CTR = PRD: Time-base counter equal to the specified period (TBCTR = TBPRD).

- CTR = Zero: Time-base counter equal to zero (TBCTR = 0x00).

- Configure the rate of the time-base clock; a prescaled version of the ePWM clock (EPWMCLK). This

allows the time-base counter to increment/decrement at a slower rate.

- **NOTE:** The Type 4 ePWM clocking varies from previous ePWM types . Prior to the Type 4 ePWM, the time-base submodule was clocked directly by the system clock (SYSCLKOUT) . On this version of the ePWM, there is a divider (EPWMCLKDIV) of the system clock which defaults to EPWMCLK = SYSCLKOUT/2

| Signal     | Description                                                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CTR = PRD  | Time-base counter equal to the specified period.                                                                                                                                           |

|            | This signal is generated whenever the counter value is equal to the active period register value. That is when TBCTR = TBPRD.                                                              |

| CTR = Zero | Time-base counter equal to zero                                                                                                                                                            |

|            | This signal is generated whenever the counter value is zero. That is when TBCTR equals 0x00.                                                                                               |

| CTR = CMPB | Time-base counter equal to active counter-compare B register (TBCTR = CMPB).                                                                                                               |

|            | This event is generated by the counter-compare submodule and used by the synchronization out logic                                                                                         |

| CTR_dir    | Time-base counter direction.                                                                                                                                                               |

|            | Indicates the current direction of the ePWM's time-base counter. This signal is high when the counter is increasing and low when it is decreasing.                                         |

| CTR_max    | Time-base counter equal max value. (TBCTR = 0xFFFF)                                                                                                                                        |

|            | Generated event when the TBCTR value reaches its maximum value. This signal is only used only as a status bit                                                                              |

| TBCLK      | Time-base clock.                                                                                                                                                                           |

|            | This is a prescaled version of the ePWM clock (EPWMCLK) and is used by all submodules within the ePWM. This clock determines the rate at which time-base counter increments or decrements. |

#### Table 15-2. Key Time-Base Signals (continued)

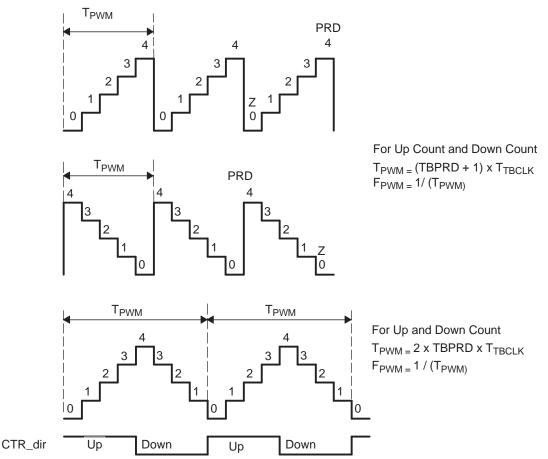

# 15.4.3 Calculating PWM Period and Frequency

The frequency of PWM events is controlled by the time-base period (TBPRD) register and the mode of the time-base counter. Figure 15-6 shows the period ( $T_{pwm}$ ) and frequency ( $F_{pwm}$ ) relationships for the up-count, down-count, and up-down-count time-base counter modes when the period is set to 4 (TBPRD = 4). The time increment for each step is defined by the time-base clock (TBCLK) which is a prescaled version of the ePWM clock (EPWMCLK).

The time-base counter has three modes of operation selected by the time-base control register (TBCTL):

## • Up-Down-Count Mode:

In up-down-count mode, the time-base counter starts from zero and increments until the period (TBPRD) value is reached. When the period value is reached, the time-base counter then decrements until it reaches zero. At this point the counter repeats the pattern and begins to increment.

# • Up-Count Mode:

In this mode, the time-base counter starts from zero and increments until it reaches the value in the period register (TBPRD). When the period value is reached, the time-base counter resets to zero and begins to increment once again.

## Down-Count Mode:

In down-count mode, the time-base counter starts from the period (TBPRD) value and decrements until it reaches zero. When it reaches zero, the time-base counter is reset to the period value and it begins to decrement once again.

# Figure 15-6. Time-Base Frequency and Period

## 15.4.3.1 Time-Base Period Shadow Register

The time-base period register (TBPRD) has a shadow register. Shadowing allows the register update to be synchronized with the hardware. The following definitions are used to describe all shadow registers in the ePWM module:

## Active Register

The active register controls the hardware and is responsible for actions that the hardware causes or invokes.

## • Shadow Register

The shadow register buffers or provides a temporary holding location for the active register. It has no direct effect on any control hardware. At a strategic point in time the shadow register's content is transferred to the active register. This prevents corruption or spurious operation due to the register being asynchronously modified by software.

The memory address of the shadow period register is the same as the active register. Which register is written to or read from is determined by the TBCTL[PRDLD] bit. This bit enables and disables the TBPRD shadow register as follows:

## • Time-Base Period Shadow Mode:

The TBPRD shadow register is enabled when TBCTL[PRDLD] = 0. Reads from and writes to the TBPRD memory address go to the shadow register. The shadow register contents are transferred to the active register (TBPRD (Active)  $\leftarrow$  TBPRD (shadow)) when the time-base counter equals zero (TBCTR = 0x00) and/or a sync event as determined by the TBCTL2[PRDLDSYNC] bit. The PRDLDSYNC bit is valid only if TBCTL[PRDLD] = 0. By default the TBPRD shadow register is enabled. The sources for the SYNC input is explained in Section 15.4.3.3.

Counter-Compare (CC) Submodule

Software force loading of contents from shadow register to active register is possible by using GLDCTL2[GFRCLD]. The GLDCTL2 register can also be linked across multiple PWM modules by using EPWMXLINK[GLDCTL2LINK]. This, along with the one-shot load mode feature discussed above, provides a method to correctly update multiple PWM registers in one or more PWM modules at certain PWM events or, if desired, in the same clock cycle. This is very useful in variable frequency applications and/or multi-phase interleaved applications.

# 15.5 Counter-Compare (CC) Submodule

Figure 15-13 illustrates the counter-compare submodule within the ePWM.

# Figure 15-13. Counter-Compare Submodule

# 15.5.1 Purpose of the Counter-Compare Submodule

The counter-compare submodule takes as input the time-base counter value. This value is continuously compared to the counter-compare A (CMPA) counter-compare B (CMPB) counter-compare C (CMPC) and counter-compare D (CMPD) registers. When the time-base counter is equal to one of the compare registers, the counter-compare unit generates an appropriate event.

The counter-compare:

- Generates events based on programmable time stamps using the CMPA, CMPB, CMPC and CMPD registers

- CTR = CMPA: Time-base counter equals counter-compare A register (TBCTR = CMPA)

- CTR = CMPB: Time-base counter equals counter-compare B register (TBCTR = CMPB)

- CTR = CMPC: Time-base counter equals counter-compare C register (TBCTR = CMPC)

- CTR = CMPD: Time-base counter equals counter-compare D register (TBCTR = CMPD)

- Controls the PWM duty cycle if the action-qualifier submodule is configured appropriately using counter-compare A (CMPA) & counter-compare B (CMPB)

- Shadows new compare values to prevent corruption or glitches during the active PWM cycle

# 15.5.2 Controlling and Monitoring the Counter-Compare Submodule

The counter-compare submodule operation is shown in Figure 15-14.

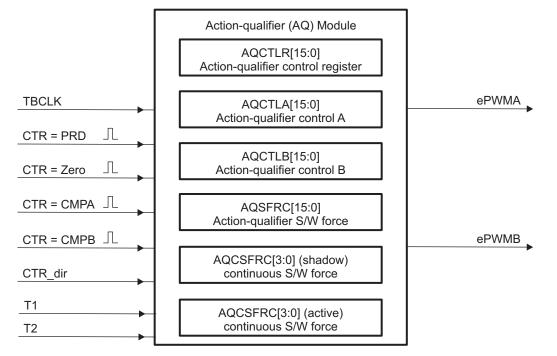

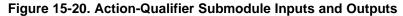

Figure 15-19. Action-Qualifier Submodule

The action-qualifier submodule has the most important role in waveform construction and PWM generation. It decides which events are converted into various action types, thereby producing the required switched waveforms at the EPWMxA and EPWMxB outputs.

# 15.6.1 Purpose of the Action-Qualifier Submodule

The action-qualifier submodule is responsible for the following:

- Qualifying and generating actions (set, clear, toggle) based on the following events:

- CTR = PRD: Time-base counter equal to the period (TBCTR = TBPRD).

- CTR = Zero: Time-base counter equal to zero (TBCTR = 0x00)

- CTR = CMPA: Time-base counter equal to the counter-compare A register (TBCTR = CMPA)

- CTR = CMPB: Time-base counter equal to the counter-compare B register (TBCTR = CMPB)

- T1, T2 events: Trigger events based on comparator, trip or syncin events

- Managing priority when these events occur concurrently

- Providing independent control of events when the time-base counter is increasing and when it is decreasing

# 15.6.2 Action-Qualifier Submodule Control and Status Register Definitions

The action-qualifier submodule operation is shown in the figure below and monitored via the registers in Section 15.15.

For convenience, the possible input events are summarized again in the table below.

| •                     |                                                  | sie input Events   |

|-----------------------|--------------------------------------------------|--------------------|

| Signal                | Description                                      | Registers Compared |

| CTR = PRD             | Time-base counter equal to the period value      | TBCTR = TBPRD      |

| CTR = Zero            | Time-base counter equal to zero                  | TBCTR = 0x00       |

| CTR = CMPA            | Time-base counter equal to the counter-compare A | TBCTR = CMPA       |

| CTR = CMPB            | Time-base counter equal to the counter-compare B | TBCTR = CMPB       |

| T1 event              | Based on comparator, trip or syncin events       | None               |

| T2 event              | Based on comparator, trip or syncin events       | None               |

| Software forced event | Asynchronous event initiated by software         |                    |

| Table 15-3. Action-Qualifier | Submodule  | Possible  | Input Events |

|------------------------------|------------|-----------|--------------|

|                              | ousinouulo | 1 0001010 | Inpat Eronto |

The software forced action is a useful asynchronous event. This control is handled by the AQSFRC and AQCSFRC registers.

The action-qualifier submodule controls how the two outputs EPWMxA and EPWMxB behave when a particular event occurs. The event inputs to the action-qualifier submodule are further qualified by the counter direction (up or down). This allows for independent action on outputs on both the count-up and count-down phases.

The possible actions imposed on outputs EPWMxA and EPWMxB are:

• Set High:

Set output EPWMxA or EPWMxB to a high level.

• Clear Low:

Set output EPWMxA or EPWMxB to a low level.

Toggle:

If EPWMxA or EPWMxB is currently pulled high, then pull the output low. If EPWMxA or EPWMxB is currently pulled low, then pull the output high.

• Do Nothing:

Keep outputs EPWMxA and EPWMxB at same level as currently set. Although the "Do Nothing" option

STRUMENTS

Texas

prevents an event from causing an action on the EPWMxA and EPWMxB outputs, this event can still trigger interrupts and ADC start of conversion. See the description in the Section 15.10 for details.

Actions are specified independently for either output (EPWMxA or EPWMxB). Any or all events can be configured to generate actions on a given output. For example, both CTR = CMPA and CTR = CMPB can operate on output EPWMxA. All qualifier actions are configured via the control registers found at the end of this section.

For clarity, the drawings in this document use a set of symbolic actions. These symbols are summarized in Figure 15-21. Each symbol represents an action as a marker in time. Some actions are fixed in time (zero and period) while the CMPA and CMPB actions are moveable and their time positions are programmed via the counter-compare A and B registers, respectively. To turn off or disable an action, use the "Do Nothing option"; it is the default at reset.

| S/W     | тв с   | Counter                | equals                | i      | Trigger                 | <sup>-</sup> Events | Actions    |

|---------|--------|------------------------|-----------------------|--------|-------------------------|---------------------|------------|

| force   | Zero   | Comp<br>A              | Comp<br>B             | Period | T1                      | T2                  |            |

| sw<br>× | Z<br>× | $\stackrel{CA}{	imes}$ | $\overset{CB}{	imes}$ | P<br>× | $\stackrel{T1}{\times}$ | T2<br>×             | Do Nothing |

| sw<br>★ | Z<br>▼ | CA<br>▼                | CB<br>▼               | ₽<br>¥ | T1<br>▼                 | T2<br>▼             | Clear Lo   |

| sw      | Z      | CA<br>▲                | CB<br>▲               | P      | <b>T1</b> ▲             | T2<br>▲             | Set Hi     |

| SW      | Z      | CA                     | СВ                    | Р      | T1                      | T2                  | Toggle     |

Figure 15-21. Possible Action-Qualifier Actions for EPWMxA and EPWMxB Outputs

The Action Qualifier Trigger Event Source Selection register (AQTSRCSEL) is used to select the source for T1 and T2 events. T1/T2 selection and configuration of a trip/digital-compare event in Action Qualifier submodule is independent of the configuration of that event in the Trip-Zone submodule. A particular trip event may or may not be configured to cause trip action in the Trip Zone submodule, but the same event can be used by the Action Qualifier to generate T1/T2 for controlling PWM generation.

# 15.6.5 Waveforms for Common Configurations

**NOTE:** The waveforms in this document show the behavior of the ePWMs for a static compare register value. In a running system, the active compare registers (CMPA and CMPB) are typically updated from their respective shadow registers once every period. The user specifies when the update will take place; either when the time-base counter reaches zero or when the time-base counter reaches period. There are some cases when the action based on the new value can be delayed by one period or the action based on the old value can take effect for an extra period. Some PWM configurations avoid this situation. These include, but are not limited to, the following:

#### Use up-down-count mode to generate a symmetric PWM:

- If you load CMPA/CMPB on zero, then use CMPA/CMPB values greater than or equal to 1.

- If you load CMPA/CMPB on period, then use CMPA/CMPB values less than or equal to TBPRD-1.

This means there will always be a pulse of at least one TBCLK cycle in a PWM period which, when very short, tend to be ignored by the system.

#### Use up-down-count mode to generate an asymmetric PWM:

To achieve 50%-0% asymmetric PWM use the following configuration: Load CMPA/CMPB on period and use the period action to clear the PWM and a compare-up action to set the PWM. Modulate the compare value from 0 to TBPRD to achieve 50%-0% PWM duty.

#### When using up-count mode to generate an asymmetric PWM:

To achieve 0-100% asymmetric PWM use the following configuration: Load CMPA/CMPB on TBPRD. Use the Zero action to set the PWM and a compare-up action to clear the PWM. Modulate the compare value from 0 to TBPRD+1 to achieve 0-100% PWM duty.

See the Using Enhanced Pulse Width Modulator (ePWM) Module for 0-100% Duty Cycle Control Application Report (literature number SPRAAI1)

The figure below shows how a symmetric PWM waveform can be generated using the up-down-count mode of the TBCTR. In this mode 0%-100% DC modulation is achieved by using equal compare matches on the up count and down count portions of the waveform. In the example shown, CMPA is used to make the comparison. When the counter is incrementing the CMPA match will pull the PWM output high. Likewise, when the counter is decrementing the compare match will pull the PWM signal low. When CMPA = 0, the PWM signal is low for the entire period giving the 0% duty waveform. When CMPA = TBPRD, the PWM signal is high achieving 100% duty.

When using this configuration in practice, if you load CMPA/CMPB on zero, then use CMPA/CMPB values greater than or equal to 1. If you load CMPA/CMPB on period, then use CMPA/CMPB values less than or equal to TBPRD-1. This means there will always be a pulse of at least one TBCLK cycle in a PWM period which, when very short, tend to be ignored by the system.

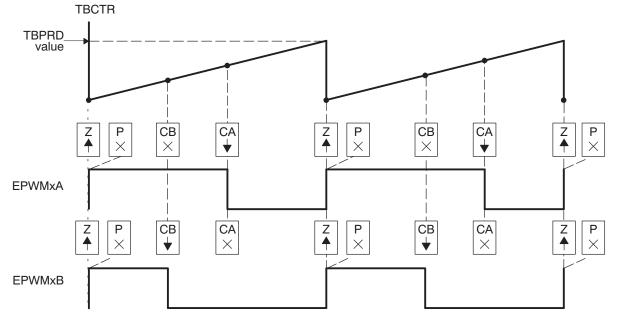

# Figure 15-25. Up, Single Edge Asymmetric Waveform, With Independent Modulation on EPWMxA and EPWMxB—Active High

A PWM period = (TBPRD + 1) ×  $T_{TBCLK}$

B Duty modulation for EPWMxA is set by CMPA, and is active high (that is, high time duty proportional to CMPA).

C Duty modulation for EPWMxB is set by CMPB and is active high (that is, high time duty proportional to CMPB).

D The "Do Nothing" actions (X) are shown for completeness, but will not be shown on subsequent diagrams.

E Actions at zero and period, although appearing to occur concurrently, are actually separated by one TBCLK period. TBCTR wraps from period to 0000.

# Figure 15-26. Up, Single Edge Asymmetric Waveform With Independent Modulation on EPWMxA and EPWMxB—Active Low

PWM period = (TBPRD + 1) ×  $T_{TBCLK}$ А

**EPWMxB**

- В Duty modulation for EPWMxA is set by CMPA, and is active low (that is, the low time duty is proportional to CMPA).

- С Duty modulation for EPWMxB is set by CMPB and is active low (that is, the low time duty is proportional to CMPB).

- D Actions at zero and period, although appearing to occur concurrently, are actually separated by one TBCLK period. TBCTR wraps from period to 0000.

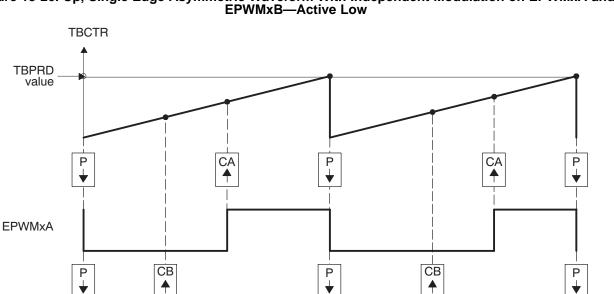

These individual flags for the CBC, OST and DCxEVTy can be used to detect the source of the EPWMxTZINT Interrupt. When multiple sources are used to generate the EPWMxTZINT interrupt, reading and clearing the flags will user to take different actions based on the specific event.

# 15.10 Event-Trigger (ET) Submodule

The key functions of the event-trigger submodule are:

- Receives event inputs generated by the time-base, counter-compare, and digital-compare submodules

- Uses the time-base direction information for up/down event qualification

- Uses prescaling logic to issue interrupt requests and ADC start of conversion at:

- Every event

- Every second event

- Up to every fifteenth event

- Provides full visibility of event generation via event counters and flags

- Allows software forcing of Interrupts and ADC start of conversion

The event-trigger submodule manages the events generated by the time-base submodule, the countercompare submodule, and the digital-compare submodule to generate an interrupt to the CPU and/or a start of conversion pulse to the ADC when a selected event occurs. Figure 15-43 illustrates where the event-trigger submodule fits within the ePWM system.

# 15.15 ePWM Registers

This section describes the Enhanced Pulse Width Modulator registers.

# 15.15.1 ePWM Base Addresses

#### Table 15-19. ePWM Base Address Table

| Device Register             | Register Name  | Start Address | End Address |

|-----------------------------|----------------|---------------|-------------|

| EPwm1Regs                   | EPWM_REGS      | 0x0000_4000   | 0x0000_40FF |

| EPwm2Regs                   | EPWM_REGS      | 0x0000_4100   | 0x0000_41FF |

| EPwm3Regs                   | EPWM_REGS      | 0x0000_4200   | 0x0000_42FF |

| EPwm4Regs                   | EPWM_REGS      | 0x0000_4300   | 0x0000_43FF |

| EPwm5Regs                   | EPWM_REGS      | 0x0000_4400   | 0x0000_44FF |

| EPwm6Regs                   | EPWM_REGS      | 0x0000_4500   | 0x0000_45FF |

| EPwm7Regs                   | EPWM_REGS      | 0x0000_4600   | 0x0000_46FF |

| EPwm8Regs                   | EPWM_REGS      | 0x0000_4700   | 0x0000_47FF |

| EPwm9Regs                   | EPWM_REGS      | 0x0000_4800   | 0x0000_48FF |

| EPwm10Regs                  | EPWM_REGS      | 0x0000_4900   | 0x0000_49FF |

| EPwm11Regs                  | EPWM_REGS      | 0x0000_4A00   | 0x0000_4AFF |

| EPwm12Regs                  | EPWM_REGS      | 0x0000_4B00   | 0x0000_4BFF |

| EPwmXbarRegs <sup>(1)</sup> | EPWM_XBAR_REGS | 0x0000_7A00   | 0x0000_7A3F |

| SyncSocRegs <sup>(1)</sup>  | SYNC_SOC_REGS  | 0x0000_7940   | 0x0000_794F |

<sup>(1)</sup> Only available on CPU1.

# 15.15.2 EPWM\_REGS Registers

Table 15-20 lists the EPWM\_REGS registers. All register offset addresses not listed in Table 15-20 should be considered as reserved locations and the register contents should not be modified.

# Table 15-20. EPWM\_REGS Registers

| Offset | Acronym   | Register Name                                                            | Write Protection                      | Section |

|--------|-----------|--------------------------------------------------------------------------|---------------------------------------|---------|

| 0h     | TBCTL     | Time Base Control Register                                               |                                       | Go      |

| 1h     | TBCTL2    | Time Base Control Register 2                                             |                                       | Go      |

| 4h     | TBCTR     | Time Base Counter Register                                               |                                       | Go      |

| 5h     | TBSTS     | Time Base Status Register                                                |                                       | Go      |

| 8h     | CMPCTL    | Counter Compare Control Register                                         |                                       | Go      |

| 9h     | CMPCTL2   | Counter Compare Control Register 2                                       |                                       | Go      |

| Ch     | DBCTL     | Dead-Band Generator Control Register                                     |                                       | Go      |

| Dh     | DBCTL2    | Dead-Band Generator Control Register 2                                   |                                       | Go      |

| 10h    | AQCTL     | Action Qualifier Control Register                                        |                                       | Go      |

| 11h    | AQTSRCSEL | Action Qualifier Trigger Event Source Select<br>Register                 |                                       | Go      |

| 14h    | PCCTL     | PWM Chopper Control Register                                             |                                       | Go      |

| 18h    | VCAPCTL   | Valley Capture Control Register                                          |                                       | Go      |

| 19h    | VCNTCFG   | Valley Counter Config Register                                           |                                       | Go      |

| 20h    | HRCNFG    | HRPWM Configuration Register                                             | EALLOW                                | Go      |

| 21h    | HRPWR     | HRPWM Power Register                                                     | EALLOW                                | Go      |

| 26h    | HRMSTEP   | HRPWM MEP Step Register                                                  | EALLOW                                | Go      |

| 27h    | HRCNFG2   | HRPWM Configuration 2 Register                                           | EALLOW                                | Go      |

| 2Dh    | HRPCTL    | High Resolution Period Control Register EALLOW                           |                                       | Go      |

| 2Eh    | TRREM     | Translator High Resolution Remainder Register EALLOW                     |                                       | Go      |

| 34h    | GLDCTL    | Global PWM Load Control Register EALLOW                                  |                                       | Go      |

| 35h    | GLDCFG    | Global PWM Load Config Register EALLOW                                   |                                       | Go      |

| 38h    | EPWMXLINK | EPWMx Link Register                                                      |                                       | Go      |

| 40h    | AQCTLA    | Action Qualifier Control Register For Output A                           |                                       | Go      |

| 41h    | AQCTLA2   | Additional Action Qualifier Control Register For<br>Output A             |                                       | Go      |

| 42h    | AQCTLB    | Action Qualifier Control Register For Output B                           |                                       | Go      |

| 43h    | AQCTLB2   | Additional Action Qualifier Control Register For<br>Output B             |                                       | Go      |

| 47h    | AQSFRC    | Action Qualifier Software Force Register                                 |                                       | Go      |

| 49h    | AQCSFRC   | Action Qualifier Continuous S/W Force Register                           | · · · · · · · · · · · · · · · · · · · | Go      |

| 50h    | DBREDHR   | Dead-Band Generator Rising Edge Delay High<br>Resolution Mirror Register |                                       | Go      |

| 51h    | DBRED     | Dead-Band Generator Rising Edge Delay High<br>Resolution Mirror Register |                                       | Go      |

| 52h    | DBFEDHR   | Dead-Band Generator Falling Edge Delay High<br>Resolution Register       |                                       | Go      |

| 53h    | DBFED     | Dead-Band Generator Falling Edge Delay Count<br>Register                 |                                       | Go      |

| 60h    | TBPHS     | Time Base Phase High                                                     |                                       | Go      |

| 62h    | TBPRDHR   | Time Base Period High Resolution Register                                |                                       | Go      |

| 63h    | TBPRD     | Time Base Period Register                                                |                                       | Go      |

| 6Ah    | СМРА      | Counter Compare A Register                                               |                                       | Go      |

| 6Ch    | СМРВ      | Compare B Register                                                       |                                       | Go      |

| 6Fh    | CMPC      | Counter Compare C Register                                               |                                       | Go      |

| 71h    | CMPD      | Counter Compare D Register                                               |                                       | Go      |

| Table 15-20. EPWM | _REGS Registers | (continued) |

|-------------------|-----------------|-------------|

|-------------------|-----------------|-------------|

| Offset | Acronym      | Register Name                                            | Write Protection                             | Section |

|--------|--------------|----------------------------------------------------------|----------------------------------------------|---------|

| 74h    | GLDCTL2      | Global PWM Load Control Register 2                       | EALLOW                                       | Go      |

| 77h    | SWVDELVAL    | Software Valley Mode Delay Register                      |                                              | Go      |

| 80h    | TZSEL        | Trip Zone Select Register                                | EALLOW                                       | Go      |

| 82h    | TZDCSEL      | Trip Zone Digital Comparator Select Register             | EALLOW                                       | Go      |

| 84h    | TZCTL        | Trip Zone Control Register                               | EALLOW                                       | Go      |

| 85h    | TZCTL2       | Additional Trip Zone Control Register                    | EALLOW                                       | Go      |

| 86h    | TZCTLDCA     | Trip Zone Control Register Digital Compare A             | EALLOW                                       | Go      |

| 87h    | TZCTLDCB     | Trip Zone Control Register Digital Compare B             | EALLOW                                       | Go      |

| 8Dh    | TZEINT       | Trip Zone Enable Interrupt Register                      | EALLOW                                       | Go      |

| 93h    | TZFLG        | Trip Zone Flag Register                                  | · · ·                                        | Go      |

| 94h    | TZCBCFLG     | Trip Zone CBC Flag Register                              |                                              | Go      |

| 95h    | TZOSTFLG     | Trip Zone OST Flag Register                              |                                              | Go      |

| 97h    | TZCLR        | Trip Zone Clear Register                                 | EALLOW                                       | Go      |

| 98h    | TZCBCCLR     | Trip Zone CBC Clear Register                             | EALLOW                                       | Go      |

| 99h    | TZOSTCLR     | Trip Zone OST Clear Register                             | EALLOW                                       | Go      |

| 9Bh    | TZFRC        | Trip Zone Force Register                                 | EALLOW                                       | Go      |

| A4h    | ETSEL        | Event Trigger Selection Register                         |                                              | Go      |

| A6h    | ETPS         | Event Trigger Pre-Scale Register                         | Event Trigger Pre-Scale Register             |         |

| A8h    | ETFLG        | Event Trigger Flag Register                              | Event Trigger Flag Register                  |         |

| AAh    | ETCLR        | Event Trigger Clear Register                             | Event Trigger Clear Register                 |         |

| ACh    | ETFRC        | Event Trigger Force Register                             |                                              | Go      |

| AEh    | ETINTPS      | Event-Trigger Interrupt Pre-Scale Register               |                                              | Go      |

| B0h    | ETSOCPS      | Event-Trigger SOC Pre-Scale Register                     |                                              | Go      |

| B2h    | ETCNTINITCTL | Event-Trigger Counter Initialization Control<br>Register | Event-Trigger Counter Initialization Control |         |

| B4h    | ETCNTINIT    | Event-Trigger Counter Initialization Register            |                                              | Go      |

| C0h    | DCTRIPSEL    | Digital Compare Trip Select Register                     | EALLOW                                       | Go      |

| C3h    | DCACTL       | Digital Compare A Control Register                       | EALLOW                                       | Go      |

| C4h    | DCBCTL       | Digital Compare B Control Register                       | EALLOW                                       | Go      |

| C7h    | DCFCTL       | Digital Compare Filter Control Register                  | EALLOW                                       | Go      |

| C8h    | DCCAPCTL     | Digital Compare Capture Control Register                 | EALLOW                                       | Go      |

| C9h    | DCFOFFSET    | Digital Compare Filter Offset Register                   | · · ·                                        | Go      |

| CAh    | DCFOFFSETCNT | Digital Compare Filter Offset Counter Register           |                                              | Go      |

| CBh    | DCFWINDOW    | Digital Compare Filter Window Register                   |                                              | Go      |

| CCh    | DCFWINDOWCNT | Digital Compare Filter Window Counter Register           | r                                            | Go      |

| CFh    | DCCAP        | Digital Compare Counter Capture Register                 |                                              | Go      |

| D2h    | DCAHTRIPSEL  | Digital Compare AH Trip Select                           | EALLOW                                       | Go      |

| D3h    | DCALTRIPSEL  | Digital Compare AL Trip Select                           | EALLOW                                       | Go      |

| D4h    | DCBHTRIPSEL  | Digital Compare BH Trip Select                           | EALLOW                                       | Go      |

| D5h    | DCBLTRIPSEL  | Digital Compare BL Trip Select                           | EALLOW                                       | Go      |

| FDh    | HWVDELVAL    | Hardware Valley Mode Delay Register                      |                                              | Go      |

| FEh    | VCNTVAL      | Hardware Valley Counter Register                         |                                              | Go      |

Complex bit access types are encoded to fit into small table cells. Table 15-21 shows the codes that are used for access types in this section.

| Access Type     | Code      | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read Type       |           |                                                                                                                                                                                                                                                                                                              |

| R               | R         | Read                                                                                                                                                                                                                                                                                                         |

| R-0             | R<br>-0   | Read<br>Returns 0s                                                                                                                                                                                                                                                                                           |

| Write Type      |           |                                                                                                                                                                                                                                                                                                              |

| W               | W         | Write                                                                                                                                                                                                                                                                                                        |

| W1C             | W<br>1C   | Write<br>1 to clear                                                                                                                                                                                                                                                                                          |

| W1S             | W<br>1S   | Write<br>1 to set                                                                                                                                                                                                                                                                                            |

| Reset or Defaul | t Value   | 1                                                                                                                                                                                                                                                                                                            |

| -n              |           | Value after reset or the default value                                                                                                                                                                                                                                                                       |

| Register Array  | Variables |                                                                                                                                                                                                                                                                                                              |

| i,j,k,l,m,n     |           | When these variables are used in<br>a register name, an offset, or an<br>address, they refer to the value of<br>a register array where the register<br>is part of a group of repeating<br>registers. The register groups form<br>a hierarchical structure and the<br>array is represented with a<br>formula. |

| У               |           | When this variable is used in a register name, an offset, or an address it refers to the value of a register array.                                                                                                                                                                                          |

# Table 15-21. EPWM\_REGS Access Type Codes

# 15.15.2.1 TBCTL Register (Offset = 0h) [reset = 83h]

TBCTL is shown in Figure 15-93 and described in Table 15-22.

Return to the Summary Table.

Time Base Control Register

#### Figure 15-93. TBCTL Register

|           |            |          | J    | J      |        |      |       |

|-----------|------------|----------|------|--------|--------|------|-------|

| 15        | 14         | 13       | 12   | 11     | 10     | 9    | 8     |

| FREE      | _SOFT      | PHSDIR   |      | CLKDIV |        | HSPC | LKDIV |

| R/\       | V-0h       | R/W-0h   |      | R/W-0h |        | R/W  | /-1h  |

| 7         | 6          | 5        | 4    | 3      | 2      | 1    | 0     |

| HSPCLKDIV | SWFSYNC    | SYNCOSEL |      | PRDLD  | PHSEN  | CTRM | NODE  |

| R/W-1h    | R-0/W1S-0h | R/W      | /-0h | R/W-0h | R/W-0h | R/W  | /-3h  |

|           |            |          |      |        |        |      |       |

## Table 15-22. TBCTL Register Field Descriptions

| Bit   | Field     | Туре | Reset | Description                                                                                               |

|-------|-----------|------|-------|-----------------------------------------------------------------------------------------------------------|

| 15-14 | FREE_SOFT | R/W  | 0h    | Emulation Mode Bits. These bits select the behavior of the ePWM time-base counter during emulation events |

|       |           |      |       | 00: Stop after the next time-base counter increment or decrement                                          |

|       |           |      |       | 01: Stop when counter completes a whole cycle:                                                            |

|       |           |      |       | - Up-count mode: stop when the time-base counter = period (TBCTR = TBPRD)                                 |

|       |           |      |       | - Down-count mode: stop when the time-base counter = 0x00 (TBCTR = 0x00)                                  |

|       |           |      |       | - Up-down-count mode: stop when the time-base counter = 0x00 (TBCTR = 0x00)                               |

|       |           |      |       | 1x: Free run                                                                                              |

|       |           |      |       | Reset type: SYSRSn                                                                                        |

| 13    | PHSDIR    | R/W  | 0h    | Phase Direction Bit                                                                                       |

|       |           |      |       | This bit is only used when the time-base counter is configured in the up-down-count mode. The             |

|       |           |      |       | PHSDIR bit indicates the direction the time-base counter (TBCTR) will count after a synchronization       |

|       |           |      |       | event occurs and a new phase value is loaded from the phase (TBPHS) register. This is                     |

|       |           |      |       | irrespective of the direction of the counter before the synchronization event.                            |

|       |           |      |       | In the up-count and down-count modes this bit is ignored.                                                 |

|       |           |      |       | 0: Count down after the synchronization event.                                                            |

|       |           |      |       | 1: Count up after the synchronization event.<br>Reset type: SYSRSn                                        |

| Bit   | Field     | Туре    | Reset | Description                                                                                                                                                                           |

|-------|-----------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-10 | CLKDIV    | R/W     | 0h    | Time Base Clock Pre-Scale Bits                                                                                                                                                        |

|       |           |         |       | These bits select the time base clock pre-scale value (TBCLK = EPWMCLK/(HSPCLKDIV * CLKDIV):                                                                                          |

|       |           |         |       | 000: /1 (default on reset)                                                                                                                                                            |

|       |           |         |       | 001: /2                                                                                                                                                                               |

|       |           |         |       | 010: /4                                                                                                                                                                               |

|       |           |         |       | 011: /8                                                                                                                                                                               |

|       |           |         |       | 100: /16                                                                                                                                                                              |

|       |           |         |       | 101: /32                                                                                                                                                                              |

|       |           |         |       | 110: /64                                                                                                                                                                              |

|       |           |         |       | 111: /128                                                                                                                                                                             |

|       |           |         |       | Reset type: SYSRSn                                                                                                                                                                    |

| 9-7   | HSPCLKDIV | R/W     | 1h    | High Speed Time Base Clock Pre-Scale Bits                                                                                                                                             |

|       |           |         |       | These bits determine part of the time-base clock prescale value.                                                                                                                      |

|       |           |         |       | TBCLK = EPWMCLK / (HSPCLKDIV x CLKDIV). This divisor<br>emulates the HSPCLK in the TMS320x281x system as used on the<br>Event Manager (EV) peripheral.                                |

|       |           |         |       | 000: /1                                                                                                                                                                               |

|       |           |         |       | 001: /2 (default on reset)                                                                                                                                                            |

|       |           |         |       | 010: /4                                                                                                                                                                               |

|       |           |         |       | 011: /6                                                                                                                                                                               |

|       |           |         |       | 100: /8                                                                                                                                                                               |

|       |           |         |       | 101: /10                                                                                                                                                                              |

|       |           |         |       | 110: /12                                                                                                                                                                              |

|       |           |         |       | 111: /14                                                                                                                                                                              |

|       |           |         |       | Reset type: SYSRSn                                                                                                                                                                    |

| 6     | SWFSYNC   | R-0/W1S | Oh    | Software Forced Sync Pulse                                                                                                                                                            |

|       |           |         |       | 0: Writing a 0 has no effect and reads always return a 0.                                                                                                                             |

|       |           |         |       | 1: Writing a 1 forces a one-time synchronization pulse to be generated.                                                                                                               |

|       |           |         |       | SWFSYNC affects EPWMxSYNCO only when SYNCOSEL = 00.<br>Reset type: SYSRSn                                                                                                             |

| 5-4   | SYNCOSEL  | R/W     | 0h    | Sync Output Select                                                                                                                                                                    |

|       |           |         |       | 00: EPWMxSYNCI / SWFSYNC                                                                                                                                                              |

|       |           |         |       | 01: CTR = zero: Time-base counter equal to zero (TBCTR = 0x00)                                                                                                                        |

|       |           |         |       | 10: CTR = CMPB : Time-base counter equal to counter-compare B (TBCTR = CMPB)                                                                                                          |

|       |           |         |       | 11: EPWMXSYNCO is defined by TBCTL2[SYNCOSELX]<br>Reset type: SYSRSn                                                                                                                  |

| 3     | PRDLD     | R/W     | 0h    | Active Period Reg Load from Shadow Select                                                                                                                                             |

|       |           |         |       | 0: The period register (TBPRD) is loaded from its shadow register when the time-base counter, TBCTR, is equal to zero and/or a sync event as determined by the TBCTL2[PRDLDSYNC] bit. |

|       |           |         |       | A write/read to the TBPRD register accesses the shadow register.                                                                                                                      |

|       |           |         |       | 1: Immediate Mode (Shadow register bypassed): A write or read to the TBPRD register accesses the active register.<br>Reset type: SYSRSn                                               |

Table 15-22. TBCTL Register Field Descriptions (continued)

|  | www.t | i.com |

|--|-------|-------|

|--|-------|-------|

| Bit | Field   | Туре | Reset | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-----|---------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | PHSEN   | R/W  | 0h    | Counter Reg Load from Phase Reg Enable                                                                                                                                                                                                                                                                                                                                        |

|     |         |      |       | 0: Do not load the time-base counter (TBCTR) from the time-base phase register (TBPHS).                                                                                                                                                                                                                                                                                       |

|     |         |      |       | 1: Allow Counter to be loaded from the Phase register (TBPHS) and<br>shadow to active load events when an EPWMxSYNCI input signal<br>occurs or a software-forced sync signal, see bit 6.<br>Reset type: SYSRSn                                                                                                                                                                |

| 1-0 | CTRMODE | R/W  | 3h    | Counter Mode                                                                                                                                                                                                                                                                                                                                                                  |

|     |         |      |       | The time-base counter mode is normally configured once and not<br>changed during normal operation. If you change the mode of the<br>counter, the change will take effect at the next TBCLK edge and the<br>current counter value shall increment or decrement from the value<br>before the mode change. These bits set the time-base counter mode<br>of operation as follows: |

|     |         |      |       | 00: Up-count mode                                                                                                                                                                                                                                                                                                                                                             |

|     |         |      |       | 01: Down-count mode                                                                                                                                                                                                                                                                                                                                                           |

|     |         |      |       | 10: Up-down count mode                                                                                                                                                                                                                                                                                                                                                        |

|     |         |      |       | 11: Freeze counter operation (default on reset)                                                                                                                                                                                                                                                                                                                               |

| 1   |         |      |       | Reset type: SYSRSn                                                                                                                                                                                                                                                                                                                                                            |

Table 15-22. TBCTL Register Field Descriptions (continued)

# 15.15.2.3 TBCTR Register (Offset = 4h) [reset = 0h]

TBCTR is shown in Figure 15-95 and described in Table 15-24.

Return to the Summary Table.

Time Base Counter Register

| Figure 15-95. TBCTR Register |    |    |     |      |    |   |   |  |  |  |  |  |

|------------------------------|----|----|-----|------|----|---|---|--|--|--|--|--|

| 15                           | 14 | 13 | 12  | 11   | 10 | 9 | 8 |  |  |  |  |  |

|                              |    |    | TBO | CTR  |    |   |   |  |  |  |  |  |

| R/W-0h                       |    |    |     |      |    |   |   |  |  |  |  |  |

| 7                            | 6  | 5  | 4   | 3    | 2  | 1 | 0 |  |  |  |  |  |

|                              |    |    | TBO | CTR  |    |   |   |  |  |  |  |  |

|                              |    |    | R/V | V-0h |    |   |   |  |  |  |  |  |

|                              |    |    |     |      |    |   |   |  |  |  |  |  |

## Table 15-24. TBCTR Register Field Descriptions

| Bit  | Field | Туре | Reset | Description                                      |

|------|-------|------|-------|--------------------------------------------------|

| 15-0 | TBCTR | R/W  | 0h    | Time Base Counter Register<br>Reset type: SYSRSn |

# 15.15.2.5 CMPCTL Register (Offset = 8h) [reset = 0h]

CMPCTL is shown in Figure 15-97 and described in Table 15-26.

Return to the Summary Table.

Counter Compare Control Register

# Figure 15-97. CMPCTL Register

|          |                    |        | •         |       | •    |           |           |  |  |

|----------|--------------------|--------|-----------|-------|------|-----------|-----------|--|--|

| 15       | 14                 | 13     | 12        | 11    | 10   | 9         | 8         |  |  |

| RESE     | RVED               | LOAD   | BSYNC     | LOADA | SYNC | SHDWBFULL | SHDWAFULL |  |  |

| R-0      | )-0h               | R/V    | V-0h      | R/W   | /-0h | R-0h R-0h |           |  |  |

| 7        | 6                  | 5      | 4         | 3     | 2    | 1         | 0         |  |  |

| RESERVED | RESERVED SHDWBMODE |        | SHDWAMODE | LOADB | MODE | LOADAMODE |           |  |  |

| R-0-0h   | R/W-0h             | R-0-0h | R/W-0h    | R/W   | /-0h | R/V       | V-0h      |  |  |

# Table 15-26. CMPCTL Register Field Descriptions

| Bit   | Field     | Туре | Reset | Description                                                                                                                                                                                                                      |

|-------|-----------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-14 | RESERVED  | R-0  | 0h    | Reserved                                                                                                                                                                                                                         |

| 13-12 | LOADBSYNC | R/W  | 0h    | Shadow to Active CMPB Register Load on SYNC event                                                                                                                                                                                |

|       |           |      |       | 00: Shadow to Active Load of CMPB:CMPBHR occurs according to LOADBMODE (bits 1,0) (same as legacy)                                                                                                                               |

|       |           |      |       | 01: Shadow to Active Load of CMPB:CMPBHR occurs both according to LOADBMODE bits and when SYNC occurs                                                                                                                            |

|       |           |      |       | 10: Shadow to Active Load of CMPB:CMPBHR occurs only when a SYNC is received                                                                                                                                                     |

|       |           |      |       | 11: Reserved                                                                                                                                                                                                                     |

|       |           |      |       | Note: This bit is valid only if CMPCTL[SHDWBMODE] = 0.<br>Reset type: SYSRSn                                                                                                                                                     |

| 11-10 | LOADASYNC | R/W  | 0h    | Shadow to Active CMPA Register Load on SYNC event                                                                                                                                                                                |

|       |           |      |       | 00: Shadow to Active Load of CMPA:CMPAHR occurs according to LOADAMODE (bits 1,0) (same as legacy)                                                                                                                               |

|       |           |      |       | 01: Shadow to Active Load of CMPA:CMPAHR occurs both according to LOADAMODE bits and when SYNC occurs                                                                                                                            |

|       |           |      |       | 10: Shadow to Active Load of CMPA:CMPAHR occurs only when a SYNC is received                                                                                                                                                     |

|       |           |      |       | 11: Reserved                                                                                                                                                                                                                     |

|       |           |      |       | Note: This bit is valid only if CMPCTL[SHDWAMODE] = 0.<br>Reset type: SYSRSn                                                                                                                                                     |

| 9     | SHDWBFULL | R    | 0h    | Counter-compare B (CMPB) Shadow Register Full Status Flag                                                                                                                                                                        |

|       |           |      |       | This bit self clears once a loadstrobe occurs.                                                                                                                                                                                   |

|       |           |      |       | 0: CMPB shadow FIFO not full yet                                                                                                                                                                                                 |