# OV6620 SINGLE-CHIP CMOS CIF COLOR DIGITAL CAMERA OV6120 SINGLE-CHIP CMOS CIF B&W DIGITAL CAMERA

#### **Features**

- 101,376 pixels, 1/4" lens, CIF/QCIF format

- Progressive scan read out

- Data format YCrCb 4:2:2, GRB 4:2:2, RGB Raw Data

- 8/16 bit video data: CCIR601, CCIR656, ZV port

- Wide dynamic range, anti-blooming, zero smearing

- Electronic exposure / Gain / white balance control

- Image enhancement brightness, contrast, gamma, saturation, sharpness, window, etc.

- Internal/external synchronization

- Frame exposure/line exposure option

- 5-Volt operation, low power dissipation

- < 80 mW active power

- < 10  $\mu$ A in power-save mode

- Gamma correction (0.45/0.55/1.00)

- I<sup>2</sup>C programmable (400 kb/s):

- color saturation, brightness, contrast, white balance, exposure time, gain

### **General Description**

The OV6620 (color) and OV6120 (black and white) CMOS Image sensors are single-chip video/imaging camera devices designed to provide a high level of functionality in a single, small-footprint package. Both devices incorporate a 352 x 288 image array capable of operating up to 60 frames per second image capture. Proprietary sensor technology utilizes advanced algorithms to cancel Fixed Pattern Noise (FPN), eliminate smearing, and drastically reduce blooming. All needed

camera functions including exposure control, gamma, gain, white balance, color matrix, windowing, and more, are programmable through an I<sup>2</sup>C interface. Both devices can be programmed to provide image output in either 4-, 8- or 16-bit digital formats.

Applications include: Video Conferencing, Video Phone, Video Mail, Still Image, and PC Multimedia.

\* Note: Outputs UV0-UV7 are not available on the OV6120. The inputs associated with these respective pins are still functional.

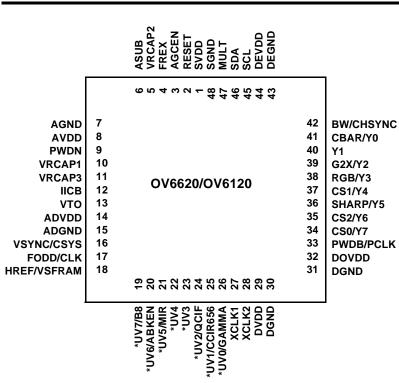

OV6620/OV6120 PIN ASSIGNMENTS

| Array Elements (CIF)<br>(QCIF)    | 356 x 292<br>(176 x 144)                             |

|-----------------------------------|------------------------------------------------------|

| Pixel Size                        | 9.0 x 8.2 μm                                         |

| Image Area                        | 3.1 x 2.5 mm                                         |

| Max Frames/Sec                    | Up to 60 FPS                                         |

| Electronic<br>Exposure            | Up to 500 : 1<br>(for selected FPS)                  |

| Scan Mode                         | progressive                                          |

| Gamma Correction                  | 0.45/.55/1.0                                         |

| Min. Illumination<br>(3000K)      | OV6620 - < 3 lux @ f1.2<br>OV6120 - < 0.5 lux @ f1.2 |

| S/N Ratio<br>(Digital Camera Out) | > 48 dB<br>(AGC = Off, Gamma = 1)                    |

| FPN                               | < 0.03% V <sub>P-P</sub>                             |

| Dark Current                      | < 0.2 nA/cm <sup>2</sup>                             |

| Dynamic Range                     | > 72 dB                                              |

| Power Supply                      | 5VDC, ±5% (Anal.)<br>5VDC or 3.3VDC (DIO)            |

| Power<br>Requirements             | < 80mW Active<br>< 30μW Standby                      |

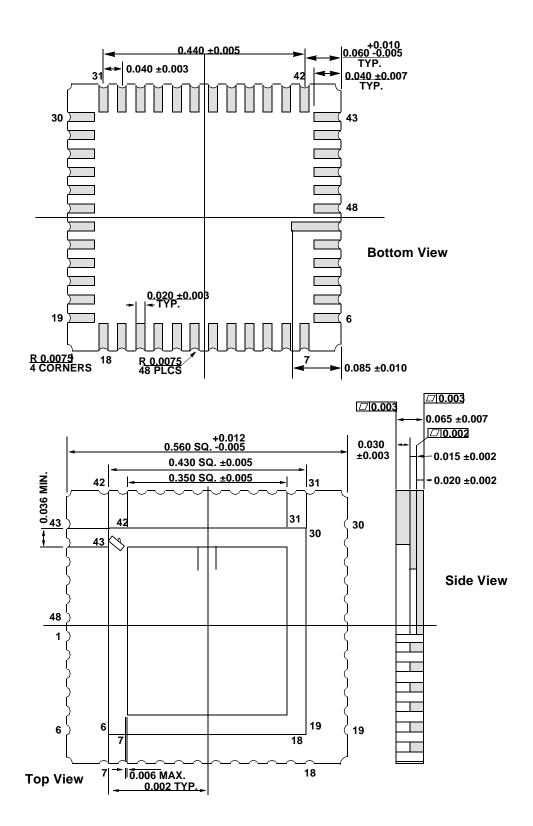

| Package                           | 48 pin LCC                                           |

OmniVision Technologies, Inc. 930 Thompson Place Sunnyvale, CA 94086 U.S.A.

Tel: (408) 733-3030 Fax: (408) 733-3061

e-mail: info@ovt.com Website: http://www.ovt.com

Table 1. Pin Description

| Pin No. | Name        | Pin Type                  | Function/Description                                                                                                                                                           |

|---------|-------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01      | SVDD        | V <sub>in</sub>           | Array power (+5VDC)                                                                                                                                                            |

| 02      | RESET       | Function<br>(Default = 0) | Chip Reset, active high                                                                                                                                                        |

| 03      | AGCEN       | Function<br>(Default = 0) | Automatic Gain Control (AGC) selection  "0" - Disable AGC  "1" - Enable AGC  NOTE: This function is disabled when OV6620/OV6120 sensor is configured in I <sup>2</sup> C mode. |

| 04      | FREX        | Function<br>(Default = 0) | Frame Exposure Control "0" - Disable Frame Exposure Control "1" - Enable Frame Exposure Control                                                                                |

| 05      | VRCAP2      | V <sub>ref</sub> (2.5V)   | Array reference. Connect to ground through 0.1 uF capacitor.                                                                                                                   |

| 06      | ASUB        | V <sub>in</sub>           | Analog substrate voltage                                                                                                                                                       |

| 07      | AGND        | V <sub>in</sub>           | Analog ground                                                                                                                                                                  |

| 08      | AVDD        | V <sub>in</sub>           | Analog power supply (+5VDC)                                                                                                                                                    |

| 09      | PWDN        | Function<br>(Default = 0) | Power down mode selection "0" - normal mode "1" - power down mode                                                                                                              |

| 10      | VrCAP1      | N/C                       | Internal voltage reference. Connect to ground through 0.1 µF capacitor.                                                                                                        |

| 11      | VrCAP3      |                           | Internal voltage reference. Connect to ground through 1 µF capacitor.                                                                                                          |

| 12      | IICB        | Function<br>(Default = 0) | I <sup>2</sup> C enable selection "0" - Enable I <sup>2</sup> C "1" - Enable autocontrol mode                                                                                  |

| 13      | VTO         | 0                         | Luminance Composite Signal Output                                                                                                                                              |

| 14      | ADVDD       | V <sub>in</sub>           | Analog power supply (+5VDC)                                                                                                                                                    |

| 15      | ADGND       | V <sub>in</sub>           | Analog signal ground                                                                                                                                                           |

| 16      | VSYNC/CSYS  | I/O                       | Vertical sync output. At power up, read as CSYS.                                                                                                                               |

| 17      | FODD/CLK    | I/O                       | Field ID FODD output or main clock output                                                                                                                                      |

| 18      | HREF/VSFRAM | I/O                       | HREF output. At power up, read as VSFRAM                                                                                                                                       |

| 19      | *UV7/B8     | I/O                       | Bit 7 of U video component output. At power up, sampled as B8.  * Note: Output UV7 is not available on the OV6120 sensor                                                       |

| 20      | *UV6/ABKEN  | I/O                       | Bit 6 of U video component output. At power up, sampled as ABKEN.  * Note: Output UV6 is not available on the OV6120 sensor                                                    |

| 21      | *UV5/MIR    | I/O                       | Bit 5 of U video component output. At power up, sampled as MIR.  * Note: Output UV5 is not available on the OV6120 sensor                                                      |

| 22      | *UV4        | I/O                       | Bit 4of U video component output.  * Note: This output (UV4) is not available on the OV6120 sensor                                                                             |

Table 1. Pin Description

| Pin No. | Name       | Pin Type                  | Function/Description                                                                                                        |

|---------|------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 23      | *UV3       | I/O                       | Bit 3 of U video component output.  * Note: This output (UV3) is not available on the OV6120 sensor                         |

| 24      | *UV2/QCIF  | I/O                       | Bit 2 of U video component output. At power up, sampled as QCIF.  * Note: Output UV2 is not available on the OV6120 sensor  |

| 25      | *UV1/CC656 | I/O                       | Bit 1 of U video component output. At power up, sampled as CC656.  * Note: Output UV1 is not available on the OV6120 sensor |

| 26      | *UV0/GAMMA | I/O                       | Bit 0 of U video component output. At power up, sampled as GAMMA.  * Note: Output UV0 is not available on the OV6120 sensor |

| 27      | XCLK1      | I                         | Crystal clock input                                                                                                         |

| 28      | XCLK2      | 0                         | Crystal clock output                                                                                                        |

| 29      | DVDD       | V <sub>in</sub>           | Digital power supply (+5VDC)                                                                                                |

| 30      | DGND       | V <sub>in</sub>           | Digital ground                                                                                                              |

| 31      | DOGND      | V <sub>in</sub>           | Digital interface output buffer ground                                                                                      |

| 32      | DOVDD      | V <sub>in</sub>           | Digital interface output buffer power supply (+5VDC)                                                                        |

| 33      | PCLK/PWDB  | I/O                       | PCLK output. At power up sampled as PWDB.                                                                                   |

| 34      | Y7/CS0     | I/O                       | Bit 7 of Y video component output. At power up, sampled as CS0.                                                             |

| 35      | Y6/CS2     | I/O                       | Bit 6 of Y video component output. At power up, sampled as CS2.                                                             |

| 36      | Y5/SHARP   | I/O                       | Bit 5 of Y video component. At power up, sampled as SHARP.                                                                  |

| 37      | Y4/CS1     | I/O                       | Bit 4 of Y video component. At power up, sampled as CS1                                                                     |

| 38      | Y3/RGB     | I/O                       | Bit 3 of Y video component output. At power up, sampled as RGB.                                                             |

| 39      | Y2/G2X     | I/O                       | Bit 2 of Y video component output. At power up, sampled as G2X.                                                             |

| 40      | Y1         | I/O                       | Bit 1 of Y video component output.                                                                                          |

| 41      | Y0/CBAR    | I/O                       | Bit 0 of Y video component output. At power up, sampled as CBAR.                                                            |

| 42      | CHSYNC/BW  | I/O                       | CHSYNC output. At power up, sampled as BW.                                                                                  |

| 43      | DEGND      | V <sub>in</sub>           | Decoder ground.                                                                                                             |

| 44      | DEVDD      | V <sub>in</sub>           | Decoder power supply (+5VDC)                                                                                                |

| 45      | SCL        | 1                         | I <sup>2</sup> C serial interface clock input                                                                               |

| 46      | SDA        | I/O                       | I <sup>2</sup> C serial interface data input and output.                                                                    |

| 47      | MULT       | Function<br>(Default = 0) | I <sup>2</sup> C slave selection "0" - Select single slave ID "1" - Enable multiple (8) slaves                              |

| 48      | SGND       | V <sub>in</sub>           | Array ground                                                                                                                |

### 1. Functional Description

(Note: References to color features do not apply to the OV6120 B&W Digital Image Sensor.)

#### 1.1 Overview

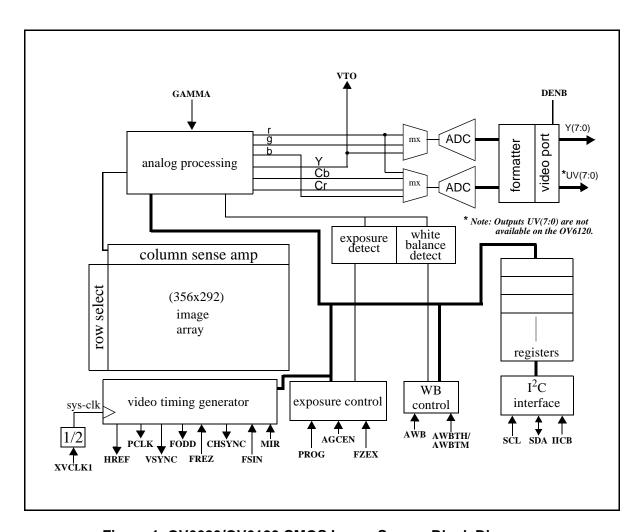

Referring to Figure 1, OV6620/OV6120 CMOS Image Sensor Block Diagram below, the OV6620 sensor includes a 356 x 292 resolution image array, an analog signal processor, dual 8-bit Analog-to-Digital converters, analog video multiplexer, digital data formatter and video port, I<sup>2</sup>C interface and registers, digital controls including timing block, exposure, and black and white balance.

The OV6620/OV6120 sensor is a 1/4-inch CMOS imaging device. The sensor contains approximately 101,376 pixels. Its design is based on a field integration read-out system with line-by-line transfer and an electronic shutter with a synchronous pixel read out scheme. The color filter of the sensor consists of a primary color RG/GB array arranged in line-alternating fashion.

Figure 1. OV6620/OV6120 CMOS Image Sensor Block Diagram

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

#### 1.2 Analog Processor Circuits

#### 1.2.1 Overview

The image is captured by the 356 x 592 pixel image array and routed to the analog processing section where the majority of signal processing occurs. This block contains the circuitry which performs color separation, matrixing, Automatic Gain Control (AGC), gamma correction, color correction, color balance, black level calibration, "knee" smoothing, aperture correction, and controls for picture luminance, chrominance, and antialias filtering. The analog video signals are based on the following formula:

$$Y = 0.59G + 0.31R + 0.11B$$

$U = R-Y$

$V = B-Y$

where R,G,B are the equivalent color components in each pixel.

A YCrCb format is also supported, based on the formula below:

$$Y = 0.59G + 0.31R + 0.11B$$

$Cr = 0.713 \times (R - Y)$

$Cb = 0.564 \times (B - Y)$

The YCrCb/RGB Raw Data signal from the analog processing section is fed to two on-chip 8-bit Analog-to-Digital (A-to-D) converters: one for the Y/RG channel and one shared by the CrCb/BG channels. The A-to-D converted data stream is further conditioned in the digital formatter. The processed signal is delivered to the digital video port through the video multiplexer which routes the user-selected 16-, 8-, or 4-bit video data the correct output pins.

The on-chip 8-bit A-to-D converters operate at up to 9 MHz, fully synchronous to the pixel rate. Actual conversion rate is set as a function of the frame rate. A-to-D black-level calibration circuitry ensures the following:

- the black level of Y/RGB is normalized to a value of 16

- the peak white level is limited to 240

- CrCb black level is 128

- Peak/Bottom is 240/16

- RGB raw data output range is 16/240

(Note: Values 0 and 255 are reserved for sync flag)

#### 1.2.2 Image Processing

The algorithm used for the electronic exposure control is based on the brightness of the full image. The exposure is optimized for a "normal" scene which assumes the subject is well lit relative to the background. In situations where the image is not well lit, the Automatic Exposure Control (AEC) White/Black ratio may be adjusted to suit the needs of the application.

Additional on-chip functions include Automatic Gain Control (AGC) which provides a gain boost of up to 24dB. White balance control enables setting of proper color temperature and can be programmed for automatic or manual operation. Separate saturation, brightness, contrast, and sharpness adjustments allow for further fine tuning of the picture quality and characteristics. The OV6620 image sensor also provides control over the White Balance ratio for increasing/decreasing the image field Red/Blue component ratio. The sensor provides a default setting which may be sufficient for many applications.

#### 1.2.3 Windowing

The windowing feature of the OV6620/OV6120 image sensors allows user-definable window sizing as required by the application. Window size setting (in pixels) ranges from 2 x 2 to 356 x 292, and can be positioned anywhere inside the 356 x 292 boundary. Note that modifying window size and/or position does not change frame or data rate. The OV6620/OV6120 imager alters the assertion of the HREF signal to be consistent with the programmed horizontal and vertical region. The default output window is 352 x 288.

#### 1.2.4 Zoom Video Port (ZV)

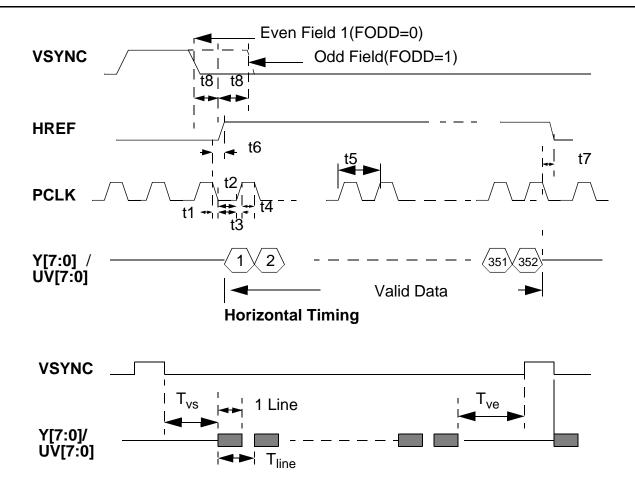

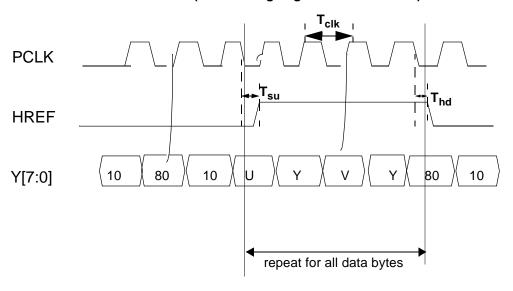

The OV6620/OV6120 image sensor includes a Zoom Video (ZV) function that supports standard ZV Port interface timing. Signals available include VSYNC, CHSYNC, PCLK and 16-bit data bus: Y[7:0] and UV[7:0]. The rising edge of PCLK clocks data into the ZV port. See Figure 2, Zoom Video Port Timing below.

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

Figure 2. Zoom Video Port Timing

#### Notes:

1. Zoom Video Port format output signal includes:

VSYNC: Vertical sync pulse.

HREF: Horizontal valid data output window.

PCLK: Pixel clock used to clock valid data and CHSYNC into Zoom V Port. Default frequency is 8.86MHz when use

17.73MHz as system clock. Rising edge of PCLK is used to clock the 16 Bit data.

Y[7:0]: 8 Bit luminance data bus.

UV[7:0]: 8 Bit chrominance data bus.

2. All timing parameters are provided in Table 13. Zoom Video Port AC Parameters

SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

#### OV6620/OV6120

#### 1.2.5 QCIF Format

A QCIF mode is available for applications where high resolution image capture is not required. When programmed in this mode, the pixel rate is reduced by one-half. Default resolution is 176 x 144 pixels and can be user-programmed for other resolutions. Refer to Table 7. QCIF Digital Output Format (YUV, beginning of line) and Table 8. QCIF Digital Output Format (RGB Raw Data, Beginning of Line) for further information.

## 1.2.6 Video Output

The video output port of the OV6620/OV6120 image sensors provides a number of output format/standard options to suit many different application requirements. Table 2. Digital Output Formats, below, indicates the output formats available. These formats are user programmable through the I<sup>2</sup>C interface (See Section 3.1 I<sup>2</sup>C Bus Protocol Format).

The OV6620/OV6120 imager supports both CCIR601 and CCIR656 output formats in the following configurations (See Table 3. 4:2:2 16-bit Format for further details):

- 16-bit, 4:2:2 format

(This mode complies with the 60/50 Hz CCIR601 timing standard. See Table 3. 4:2:2 16-bit Format below)

- 8-bit data mode

(In this mode, video information is output in Cb Y Cr Y order using the Y port only and running at twice the pixel rate during which the UV port is inactive. See Table 4. 4:2:2 8-bit Format below)

- 4-bit nibble mode

(In the nibble mode, video output data appears at bits Y4-Y7. The clock rate for the output runs at twice the normal output speed when in B/W mode, and 4 times the normal output speed in when in color mode.)

- 704 x 288 format

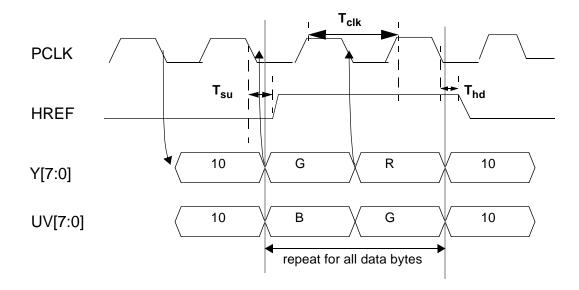

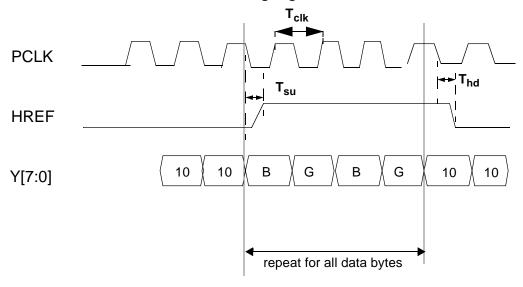

(When programmed for this mode, the OV6620/OV6120 pixel clock is doubled and the video output sequence is Y0Y0Y1Y1 ... and U0U0V0V0 ... See Figure 3, Pixel Data Bus (YUV Output), below.)

The OV6620/OV6120 imaging devices provide VSYNC, HREF, PCLK, FODD, CHSYNC as standard output video timing signals.

The OV6620/OV6120 image sensor can also be programmed to provide video output in RGB Raw Data 16-bit/8-bit/4-bit format. The output sequence is matched to the OV6620 Color Filter Pattern (See Section Figure 4. Pixel Data Bus (RGB Output), below):

- Y channel output sequence is G R G R

- UV channel output sequence is B G B G

For 8-bit RGB Raw Data video output appears on the Y channel (with an output sequence of B G R G) and the UV channel is disabled.

In RGB Raw Data CCIR656 modes, the OV6620/OV6120 imager asserts SAV (Start of Active Video) and EAV (End of Active Video) to indicate the beginning and the ending of HREF window. As a result, SAV and EAV change with the active pixel window. The 8-bit RGB raw data is also accessible without SAV and EAV information.

The OV6620/OV6120 imagers offer flexibility in YUV output format. The devices may be programmed as standard YUV 4:2:2. These devices may be configured to "swap" the U V sequence. When swapped, the UV channel output format for 16-bit configurations becomes:

- V U V U...etc.

and for 8-bit configurations becomes:

V Y U Y ...etc.

A third format is available for the 8-bit configurations and OV6620/OV6120 enables the Y/UV sequence swap:

- Y U Y V ...etc.

The OV6620 color single-IC camera can be configured for use as a black and white imaging device. In this mode, vertical resolution is greater than in color. Video data output is provided at the Y port (pins 34:41) and the UV port is tri-stated. The data (Y/RGB) output rate is equivalent to operating in 16-bit mode.

The Y/UV or RGB output byte MSB and LSB can be reverse-ordered on the OV6620/OV6120 device. The Y7 - Y0 default sequence sets Y7 as MSB and Y0 as LSB. Programming a reverse order configuration sets Y7 as LSB and Y0 is MSB, with bits Y2-Y6 reversed-ordered appropriately.

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

**Table 2. Digital Output Formats**

| Resolution                | Pixel Clock          | 352 x 288 | 704 x 288 | 176 x 144 |

|---------------------------|----------------------|-----------|-----------|-----------|

| YUV                       | 16-bit               | Y         | Y         | Υ         |

| 4:2:2                     | 8-bit                | Y         | Y         | Y         |

|                           | CCIR656              | Y         | Y         | Y         |

|                           | Nibble               | Y         | Y         | Y         |

| RGB                       | 16-bit               | Y         | Y         | Y         |

|                           | 8-bit                | Y         | Y         | Y         |

|                           | CCIR656 <sup>1</sup> | Y         | Y         | Y         |

|                           | Nibble               | Y         | Y         | Υ         |

| Y/UV                      | 16-bit               |           |           |           |

| swap <sup>2</sup>         | 8-bit                | Y         | Υ         | Y         |

| U/V                       | YUV <sup>3</sup>     | Y         | Y         | Y         |

| swap                      | RGB <sup>4</sup>     | Y         | Y         | Y         |

| YG                        | 16-bit               | Y         | Υ         | Υ         |

|                           | 8-bit                |           |           |           |

| One                       | 16-bit               | Y         |           |           |

| Line                      | 8-bit                |           |           |           |

| MSB/LSB swap <sup>5</sup> |                      | Y         | Υ         | Y         |

#### Notes:

("Y" indicates mode/combination is supported by OV6620/OV6120.)

- 1. When in RGB CCIR656 format, output is 8 bits. SAV and EAV are inserted at the beginning and ending of HREF, which synchronize the acquisition of Vsync and Hsync. In this format, an 8-bit data bus configuration (without VSYNC and CHSYNC) may be used.

- 2. Y/UV swap is valid only in 8-bit mode. Y channel output sequence is Y U Y V...

- 3. In YUV format, U/V swap means UV channel output sequence swap. V U V U... for 16 bit; V Y U Y ... for 8-bit.

- 4. In RGB format, U/V swap means neighbor row B R output sequence swap. Refer to RGB raw data output format for further details

**Table 3. 4:2:2 16-bit Format**

| Data Bus | Pixel Byte Sequence |    |    |    |    |    |  |  |  |  |

|----------|---------------------|----|----|----|----|----|--|--|--|--|

| Y7       | Y7                  | Y7 | Y7 | Y7 | Y7 | Y7 |  |  |  |  |

| Y6       | Y6                  | Y6 | Y6 | Y6 | Y6 | Y6 |  |  |  |  |

| Y5       | Y5                  | Y5 | Y5 | Y5 | Y5 | Y5 |  |  |  |  |

| Y4       | Y4                  | Y4 | Y4 | Y4 | Y4 | Y4 |  |  |  |  |

| Y3       | Y3                  | Y3 | Y3 | Y3 | Y3 | Y3 |  |  |  |  |

| Y2       | Y2                  | Y2 | Y2 | Y2 | Y2 | Y2 |  |  |  |  |

| Y1       | Y1                  | Y1 | Y1 | Y1 | Y1 | Y1 |  |  |  |  |

| Y0       | Y0                  | Y0 | Y0 | Y0 | Y0 | Y0 |  |  |  |  |

|          |                     |    |    |    |    |    |  |  |  |  |

| UV7      | U7                  | V7 | U7 | V7 | U7 | V7 |  |  |  |  |

| UV6      | U6                  | V6 | U6 | V6 | U6 | V6 |  |  |  |  |

| UV5      | U5                  | V5 | U5 | V5 | U5 | V5 |  |  |  |  |

| UV4      | U4                  | V4 | U4 | V4 | U4 | V4 |  |  |  |  |

| UV3      | U3                  | V3 | U3 | V3 | U3 | V3 |  |  |  |  |

| UV2      | U2                  | V2 | U2 | V2 | U2 | V2 |  |  |  |  |

| UV1      | U1                  | V1 | U1 | V1 | U1 | V1 |  |  |  |  |

| UV0      | U0                  | V0 | U0 | V0 | U0 | V0 |  |  |  |  |

| Y FRAME  | 0                   | 1  | 2  | 3  | 4  | 5  |  |  |  |  |

| UV FRAME | (                   | )  | 2  | 2  | 4  | 4  |  |  |  |  |

Table 4. 4:2:2 8-bit Format

| Data Bus | Pixel Byte Sequence |     |    |    |    |    |     |    |  |

|----------|---------------------|-----|----|----|----|----|-----|----|--|

| Y7       | U7                  | Y7  | V7 | Y7 | U7 | Y7 | V7  | Y7 |  |

| Y6       | U6                  | Y6  | V6 | Y6 | U6 | Y6 | V6  | Y6 |  |

| Y5       | U5                  | Y5  | V5 | Y5 | U5 | Y5 | V5  | Y5 |  |

| Y4       | U4                  | Y4  | V4 | Y4 | U4 | Y4 | V4  | Y4 |  |

| Y3       | U3                  | Y3  | V3 | Y3 | U3 | Y3 | V3  | Y3 |  |

| Y2       | U2                  | Y2  | V2 | Y2 | U2 | Y2 | V2  | Y2 |  |

| Y1       | U1                  | Y1  | V1 | Y1 | U1 | Y1 | V1  | Y1 |  |

| Y0       | U0                  | Y0  | V0 | Y0 | U0 | Y0 | V0  | Y0 |  |

| Y FRAME  | 0                   |     | 1  |    | 2  |    | 3   |    |  |

| UV FRAME |                     | 0 1 |    |    |    |    | 2 3 |    |  |

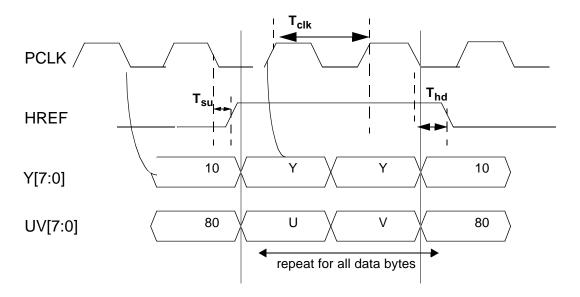

# Pixel Data 16-bit Timing (PCLK rising edge latches data bus)

Pixel Data 8-bit Timing (PCLK rising edge latches data bus)

**Note:**  $T_{clk}$  is pixel clock period. When the OV6620 system clock is 17.73 MHz,  $T_{clk}$  = 112 ns for 16-bit output;  $T_{clk}$  = 56 ns for 8-bit output.  $T_{su}$  is HREF set-up time, maximum is 15 ns;  $T_{hd}$  is HREF hold time, maximum is 15 ns.

Figure 3. Pixel Data Bus (YUV Output)

# Pixel Data 16-bit Timing PCLK rising edge latches data bus

Pixel Data 8-bit Timing PCLK rising edge latches data bus

**Note:**  $T_{clk}$  is pixel clock period. When the OV6620 system clock is 17.73MHz,  $T_{clk}$  = 112ns for 16-bit output;  $T_{clk}$  = 56ns for 8-bit output.  $T_{su}$  is HREF set-up time, maximum is 15 ns;  $T_{hd}$  is HREF hold time, maximum is 15 ns.

Figure 4. Pixel Data Bus (RGB Output)

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

MSB/LSB swap means: Default Y/UV channel output port relationship is:

**Table 5. Default Output Sequence**

|                      | MSB |    |    |    |    |    |    | LSB |

|----------------------|-----|----|----|----|----|----|----|-----|

| Output Port          | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

| Internal Output data | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

If the device is programmed for data swap, the sequence is changed to:

Table 6. Swapped MSB/LSB Output Sequence

|                      | MSB |    |    |    |    |    |    | LSB |

|----------------------|-----|----|----|----|----|----|----|-----|

| Output Port          | Y7  | Y6 | Y5 | Y4 | Y3 | Y2 | Y1 | Y0  |

| Internal Output data | Y0  | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7  |

Table 7. QCIF Digital Output Format (YUV, beginning of line)

| Pixel # | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     |

|---------|-------|-------|-------|-------|-------|-------|-------|-------|

| Υ       | Y0    | Y1    | Y2    | Y3    | Y4    | Y5    | Y6    | Y7    |

| UV      | U0,V0 | U1,V1 | U2,V2 | U3,V3 | U4,V4 | U5,V5 | U6,V6 | U7,V7 |

Y channel output Y2 Y3 Y6 Y7 Y10 Y11 ...

- UV channel output U2 V3 U6 V7 U10 V11 ...

- Every line output data number is half(176 pixels) and only one half line data (every other line, total 144 line) in one frame will be output.

Table 8. QCIF Digital Output Format (RGB Raw Data, Beginning of Line)

| Pixel # | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  |

|---------|----|----|----|----|----|----|----|----|

| Line 1  | В0 | G1 | B2 | G3 | B4 | G5 | B6 | G7 |

| Line 2  | G0 | R1 | G2 | R3 | G4 | R5 | G6 | R7 |

- 1. Default RGB two line output mode:

- Y channel output G0 R1 G4 R5 G8 R9 ...

- UV channel output B0 G1 B4 G5 B8 G9 ...

- Every line output half data(176 pixels) and all line(144 line) data in one frame will be output.

- 2. YG two line output mode:

- Y channel output G0 R1 G4 R5 G8 R9 ...

- UV channel output B0 G1 B4 G5 B8 G9 ...

- Every line outputs half data (176 pixels) and all line (144 line) data in one frame will be output.

- 3. QCIF Resolution Digital Output Format

- Y channel output Y2 Y3 Y6 Y7 Y10 Y11 ...

- UV channel output U2 V3 U6 V7 U10 V11 ...

- Every line output data number is half (176 pixels) and only one half line data (every other line, total 144 line) in one frame will be output.

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

#### Table 9. RGB Raw Data Format

| R\C | 1               | 2               | 3               | 4               | 353 | 354 | 355 | 356 |

|-----|-----------------|-----------------|-----------------|-----------------|-----|-----|-----|-----|

| 1   | B <sub>11</sub> | G <sub>12</sub> | B <sub>13</sub> | G <sub>14</sub> | В   | G   | В   | G   |

| 2   | G <sub>21</sub> | R <sub>22</sub> | G <sub>23</sub> | R <sub>24</sub> | G   | R   | G   | R   |

| 3   | B <sub>31</sub> | G <sub>32</sub> | B <sub>33</sub> | G <sub>34</sub> | В   | G   | В   | G   |

| 4   | G <sub>41</sub> | R <sub>42</sub> | G <sub>43</sub> | R <sub>44</sub> | G   | R   | G   | R   |

| 5   | B <sub>51</sub> | G <sub>52</sub> | B <sub>53</sub> | G <sub>54</sub> | В   | G   | В   | G   |

|     |                 |                 |                 |                 |     |     |     |     |

| 289 | В               | G               | В               | G               | В   | G   | В   | G   |

| 290 | G               | R               | G               | R               | G   | R   | G   | R   |

| 291 | В               | G               | В               | G               | В   | G   | В   | G   |

| 292 | G               | R               | G               | R               | G   | R   | G   | R   |

#### Notes:

A. Y port output data sequence: G R G R G R ... or G G G G ... ; UV port output data sequence: B G B G B G ... or B R B R ... ; Array Color Filter Patter is Bayer-Pattern

#### B. Output Modes

16-bit Format (HREF total 292)

#### Default mode:

- 1st HREF Y channel output unstable data, UV output  $\rm B_{11}~G_{12}~B_{13}~G_{14}~....$

- 2nd HREF Y channel output  $G_{21}$   $R_{22}$   $G_{23}$   $R_{24}$  ..., UV output  $B_{11}$   $G_{12}$   $B_{13}$   $G_{14}$  ...

- 3rd HREF Y channel output  $G_{21}$   $R_{22}$   $G_{23}$   $R_{24}$  ..., UV output  $B_{31}$   $G_{23}$   $B_{33}$   $G_{34}$  ....

- Every line of data is output twice.

#### YG mode:

- 1st HREF Y and UV output unstable data.

- 2nd HREF Y channel output  $G_{21}$   $G_{12}$   $G_{23}$   $G_{14}$  ..., UV output  $B_{11}$   $R_{22}$   $B_{13}$   $R_{24}$  ...

- 3rd HREF Y is  $\mathrm{G}_{21}$   $\mathrm{G}_{32}$   $\mathrm{G}_{23}$   $\mathrm{G}_{34}$  ..., UV channel is  $\mathrm{B}_{31}$   $\mathrm{R}_{22}$   $\mathrm{B}_{33}$   $\mathrm{R}_{24}$  ...

- Every line data output twice.

#### One line mode:

- 1st HREF Y channel output  $\mathsf{B}_{11}~\mathsf{G}_{12}~\mathsf{B}_{13}~\mathsf{G}_{14}...,$

- 2nd HREF Y channel output G<sub>21</sub> R<sub>22</sub> G<sub>23</sub> R<sub>24</sub> ...,

- UV channel tri-state.

#### 8-bit Format (HREF total 292)

- 1st HREF Y channel output unstable data.

- 2nd HREF Y channel output B11 G21 R22 G12 ...

- 3rd HREF Y channel output B31 G21 R22 G32 ..., etc.

- PCLK timing is double and PCLK rising edge latch data bus. UV channel tri-state. Every line data output twice.

#### 4-bit Nibble Mode Output Format

- Uses higher 4 bits of Y port (Y[7:4]) as output port.

- Supports YCrCb/RGB data, CCIR601/CCIR656 timing, Color/B&W.

- Output sequence: High order 4 bits followed by lower order 4 bits

Y0h Y0l Y1h Y1l ...

U0h U0l V0h V0l ...

For B/W or one-line RGB raw data, the output data clock speed is doubled. For color YUV, output clock is four times that of the 16-bit output data. In color mode, sensor must be set to 8-bit mode, and the nibble timing, clock divided by 2.

- Output sequence: U0h U0l Y0h Y0l V0h V0l Y1h Y1l ...

SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

#### OV6620/OV6120

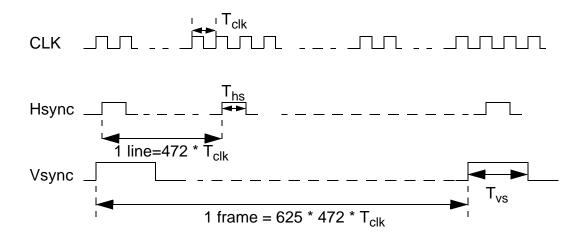

#### 1.2.7 Slave Mode Operation

The OV6620/OV6120 sensors can be programmable to operate in slave mode configuration (COMI[6] = 1, default is master mode). HSYNC and VSYNC output signals are provided.

When used as a slave device, the external master must provide the OV6620/OV6120 imager with the following:

- 1. System clock CLK to XCLK1 pin;

- 2. Horizontal sync, Hsync, to CHSYNC pin, positive assertion;

- Vertical frame sync, Vsync, to VSYNC pin, positive assertion

When in slave mode, the OV6620/OV6120 tri-states CHSYNC (pin 42) and VSYNC (pin 16) output pins, which may then be used as input pins. To synchronize multiple devices, the OV6620/OV6120 image sensors use external system clock, CLK, to synchronize external horizontal sync, HSYNC, which is then used to synchronize external vertical frame sync, Vsync. See Figure 5, Slave Mode External Sync Timing for timing considerations.

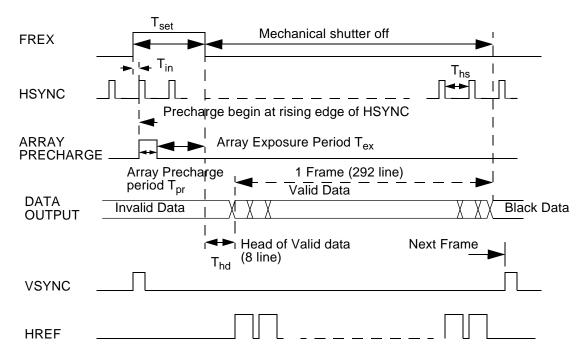

#### 1.2.8 Frame Exposure Mode

The OV6620/OV6120 sensors support frame exposure mode when programmed for Progressive Scan. FREX (pin 4) is asserted by an external master device to set exposure time. When FREX = 1, the OV6620/OV6120 pixel array will be quickly precharged. Based on the external master's assertion of FREX, the OV6620/OV6120 devices capture the image. When the master de-asserts FREX (FREX = 0), the video output data stream is delivered to the OV6620/OV6120 output port in a line-by-line manner.

It should be noted that FREX must remain active long enough to ensure the complete image array has been precharged.

When data is being output from the OV6620/OV6120 image sensor, care must be taken so as not to expose the image array to light. This may affect the integrity of the image data captured. A mechanical shutter synchronized with the frame exposure rate can be used to minimize this situation. Frame exposure mode timing is shown in Section Figure 6. Frame Exposure Timing below.

#### 1.2.9 **Reset**

The OV6620/OV6120 image sensors include a RESET pin (pin 2) which forces a complete hardware reset when

pulled high (Vcc). When a hardware reset occurs, the OV6620/OV6120 sensor clears all registers or sets them to their default values. Reset may also be initiated through the  $I^2C$  interface.

#### 1.2.10 Power Down Mode

Two methods are available for placing the OV6620/ OV6120 devices into power-down mode: hardware power down and I<sup>2</sup>C/software power down.

To initiate hardware power down the PWDN pin (pin 9) must be tied to high (+5VDC). When this occurs, the OV6620/OV6120 internal device clock is halted and all internal registers (except I<sup>2</sup>C registers) are reset. In this mode, current draw is less than 10uA.

Executing a software power down through the  $I^2C$  interface suspends internal circuit activity, but does halt the device clock. In this mode, current requirements drop to less than 1mA.

# 1.2.11 Configuring the OV6620/OV6120 Image Sensors

Two methods are provided for configuring the OV6620/OV6120 ICs for specific application requirements.

At power up, the OV6620/OV6120 sensors read the status of certain pins to determine what, if any, power up default settings are requested. Once the reading of the external pins is completed, the device configures its internal registers according to the specified pins. Not all device functions are available for configuration through external pin.

A more flexible and comprehensive method for configuring the OV6620/OV6120 ICs is to use its on-chip I $^2$ C register programming capability. The I $^2$ C interface provides access to all of the device's programmable internal registers. See Section 3.1 I $^2$ C Bus Protocol Format for further details about using the I $^2$ C interface on the OV6620/OV6120 camera device.

#### Notes:

- 1.  $T_{hs}$  > 6 \*  $T_{clk}$  (2)  $T_{hs}$  <  $T_{vs}$  < 472 \*  $T_{clk}$  2. Hsync period is 472 \* CLK

- 3. Vsync period is 625 \* 472 \* CLK

- 4. OV6620 will be stable after 1 frame. (2nd Vsync).

Figure 5. Slave Mode External Sync Timing

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

Note:  $T_{pr} = 292^* 4 * T_{clk}$ ,  $T_{clk}$  is internal pixel period. For default 17.73 MHz,  $T_{clk} = 112$  us. If CLK[5:0] set to divided number,  $T_{clk}$  will increase accordingly.

Figure 6. Frame Exposure Timing

T<sub>ex</sub> is array exposure time which is decided by external master device.

$T_{in}$  is uncertain time due to using **HSYNC** rising edge synchronize **FREX**,  $T_{in} < T_{hs}$ After **FREX**=0, there are 8 line data output before valid data output.  $T_{hd} = 4 * T_{hs}$ . Valid data is output when **HRE**

$T_{set} = T_{in} + T_{pr} + T_{ex}$ .  $T_{set} > T_{pr} + T_{in}$ . Because  $T_{in}$  is uncertain, so exposure time setting resolution is  $T_{hs}$  (one line).

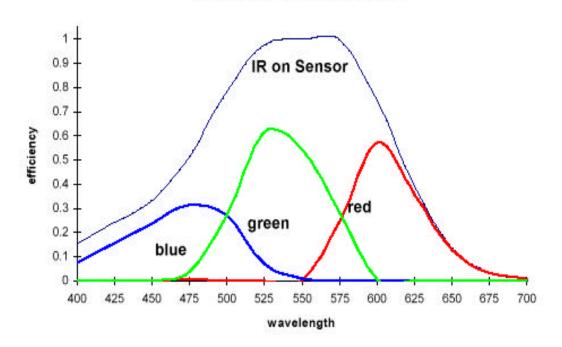

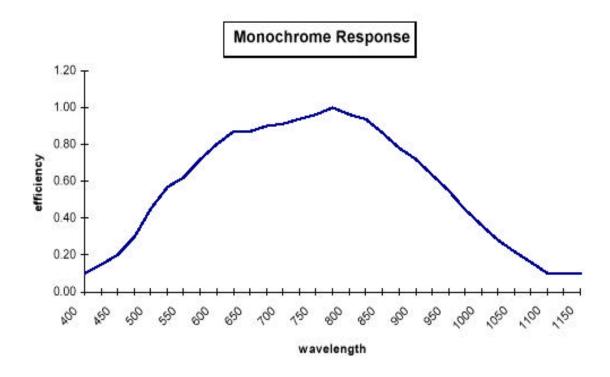

# **Normalized Spectrum Response**

# SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

# 2. Electrical Characteristics

**Table 10. DC Characteristics** ( $0^{\circ}$ C  $\leq$  TA  $\leq$  85 $^{\circ}$ C, Voltages referenced to GND)

| Symbol                  | Descriptions                                                                                | Max                  | Тур        | Min        | Units  |  |  |  |  |  |  |

|-------------------------|---------------------------------------------------------------------------------------------|----------------------|------------|------------|--------|--|--|--|--|--|--|

| Supply                  | Supply                                                                                      |                      |            |            |        |  |  |  |  |  |  |

| V <sub>DD1</sub>        | Supply voltage- internal analog (DEVDD,ADVDD,AVDD,SVDD,AOVDD,DVDD)                          | 5.25                 | 5.0        | 4.75       | V      |  |  |  |  |  |  |

| V <sub>DD2</sub>        | Supply voltage - internal digital &output digital (DOVDD)                                   | 5.5<br>3.6           | 5.0<br>3.3 | 4.5<br>3.0 | V<br>V |  |  |  |  |  |  |

| I <sub>DD1</sub>        | Supply Current (@ 50Hz frame rate & 5 volt digital I/O,25pf + 1TTL load on 16 bit data bus) | 40                   | -          | -          | mA     |  |  |  |  |  |  |

| I <sub>DD2</sub>        | Standby supply current                                                                      | 10                   | 5          | -          | uA     |  |  |  |  |  |  |

| Digital Inp             | outs                                                                                        |                      |            |            |        |  |  |  |  |  |  |

| V <sub>IL</sub>         | input voltage LOW                                                                           | 0.8                  | -          | -          | V      |  |  |  |  |  |  |

| V <sub>IH</sub>         | input voltage HIGH                                                                          | -                    | -          | 2.0        | V      |  |  |  |  |  |  |

| Cin                     | input capacitor                                                                             | 10                   | -          | -          | pF     |  |  |  |  |  |  |

| Digital Ou              | tputs - standard load 25pf, 1.2kΩ to 3.0volts                                               |                      |            |            |        |  |  |  |  |  |  |

| V <sub>OH</sub>         | output voltage HIGH                                                                         | -                    | -          | 2.4        | V      |  |  |  |  |  |  |

| V <sub>OL</sub>         | output voltage LOW                                                                          | 0.6                  | -          | -          | V      |  |  |  |  |  |  |

| I <sup>2</sup> C Inputs | - 5k pull up + 100pf                                                                        |                      |            |            |        |  |  |  |  |  |  |

| V <sub>IL</sub>         | SDA and SCL (V <sub>DD2</sub> =5V)                                                          | 1.5                  | 0          | -0.5       | V      |  |  |  |  |  |  |

| V <sub>IH</sub>         | SDA and SCL(V <sub>DD2</sub> =5V)                                                           | V <sub>dd</sub> + .5 | 5          | 3.0        | V      |  |  |  |  |  |  |

| V <sub>IL</sub>         | SDA and SCL (V <sub>DD2</sub> =3V)                                                          | 1                    | 0          | -0.5       | V      |  |  |  |  |  |  |

| V <sub>IH</sub>         | SDA and SCL(V <sub>DD2</sub> =3V)                                                           | 3.5                  | 3          | 2.5        |        |  |  |  |  |  |  |

Table 11. AC Characteristics ( $T_A=25$ °C; Vdd=5V)

| Symbol           | Descriptions                                                                     | Max | Тур             | Min | Units       |  |  |  |  |

|------------------|----------------------------------------------------------------------------------|-----|-----------------|-----|-------------|--|--|--|--|

| RGB/YCrCb output |                                                                                  |     |                 |     |             |  |  |  |  |

| Iso              | maximum sourcing current                                                         |     | 15              |     | mA          |  |  |  |  |

| Vy               | DC level at zero signal Y peak-peak 100% amplitude (without sync) sync amplitude |     | 1.2<br>1<br>0.4 |     | V<br>V<br>V |  |  |  |  |

| ADC param        | neters                                                                           |     | 1               |     |             |  |  |  |  |

| В                | analog bandwidth                                                                 |     |                 |     | MHz         |  |  |  |  |

| Φdiff            |                                                                                  |     |                 |     |             |  |  |  |  |

| DLE              | DC differential linearity error                                                  |     | 0.5             |     | LSB         |  |  |  |  |

| ILE              | DC integral linearity error                                                      |     | 1               |     | LSB         |  |  |  |  |

**Table 12. Timing Characteristics**

| Symbol                          | Descriptions                                     | Max      | Тур    | Min       | Units    |  |  |  |  |

|---------------------------------|--------------------------------------------------|----------|--------|-----------|----------|--|--|--|--|

| Oscillator & Clock in           |                                                  |          |        |           |          |  |  |  |  |

| f <sub>osc</sub>                | frequency (XCLK1,XCLK2)                          | 30       | 17.734 | 10        | MHz      |  |  |  |  |

| t <sub>r</sub> , t <sub>f</sub> | clock input rise/fall time                       | 5        |        |           | ns       |  |  |  |  |

|                                 | clock input duty cycle                           | 55       | 50     | 45        | %        |  |  |  |  |

| I <sup>2</sup> C timing         | (400kbit/s)                                      |          |        |           |          |  |  |  |  |

| t <sub>BUF</sub>                | Bus free time between STOP & START - 1.3         |          |        |           |          |  |  |  |  |

| t <sub>HD:SAT</sub>             | SCL change after START status                    | -        | -      | 0.6       | μs       |  |  |  |  |

| t <sub>LOW</sub>                | SCL low period                                   | -        | -      | 1.3       | μs       |  |  |  |  |

| t <sub>HIGH</sub>               | SCL high period                                  | -        | -      | 0.6       | μs       |  |  |  |  |

| t <sub>HD:DAT</sub>             | Data hold time                                   | -        | -      | 0         | μs       |  |  |  |  |

| t <sub>SU:DAT</sub>             | Data set-up time                                 | -        | -      | 0.1       | μs       |  |  |  |  |

| t <sub>SU:STP</sub>             | Set-up time for STOP status 0.6 µ                |          |        |           |          |  |  |  |  |

| Digital tim                     | ning                                             | <u> </u> |        |           |          |  |  |  |  |

| t <sub>pclk</sub>               | PCLK cycle time 16 bit operation 8 bit operation | -        | -      | 112<br>56 | ns<br>ns |  |  |  |  |

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

**Table 12. Timing Characteristics**

| Symbol                         | Descriptions        | Max | Тур | Min | Units |

|--------------------------------|---------------------|-----|-----|-----|-------|

| t <sub>r</sub> ,t <sub>f</sub> | PCLK rise/fall time | 15  | -   | -   | ns    |

| t <sub>pdd</sub>               | PCLK to data valid  | 15  | -   | -   | ns    |

| t <sub>phd</sub>               | PCLK to HREF delay  | 20  | 10  | 5   | ns    |

**Table 13. Zoom Video Port AC Parameters**

| Symbol | Parameter                     | Min.   | Max. |

|--------|-------------------------------|--------|------|

| t1     | PCLK fall timing              | 4 ns   | 8 ns |

| t2     | PCLK low time                 | 50 ns  |      |

| t3     | PCLK rise time                | 4 ns   | 8 ns |

| t4     | PCLK high time                | 50 ns  |      |

| t5     | PCLK period                   | 106 ns |      |

| t6     | Y/UV/HREF setup time          | 10 ns  |      |

| t7     | Y/UV/HREF hold time           | 20 ns  |      |

| t8     | VSYNC setup/hold time to HREF | 1 us   |      |

#### Notes:

- 1. In Interlaced Mode, there are Even/Odd field different (t8). When In Progressive Scan Mode, only frame timing same as Even field(t8).

- 2. After VSYNC falling edge, OV6620 will output black reference level, the line number is T<sub>vs</sub>, which is the line number between the 1st HREF rising edge after VSYNC falling edge and 1st valid data CHSYNC rising edge. Then valid data, then black reference, line number is T<sub>ve</sub>, which is the line number between last valid data CHSYNC rising edge and 1st CHSYNC rising edge after VSYNC rising edge. The black reference output line number is dependent on vertical window setting.

- 3. When in default setting,  $T_{vs}$  = 14 \*  $T_{line}$ , which is changed with register VS[7:0]. VS[7:0] step equal to 1 line.

- 4. When in default setting, T<sub>ve</sub> = 4 \* T<sub>line</sub> for Odd Field, T<sub>ve</sub> = 3 \* T<sub>line</sub> for Even Field, which is changed with register VE[7:0]. VE[7:0] step equal to 1 line.

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

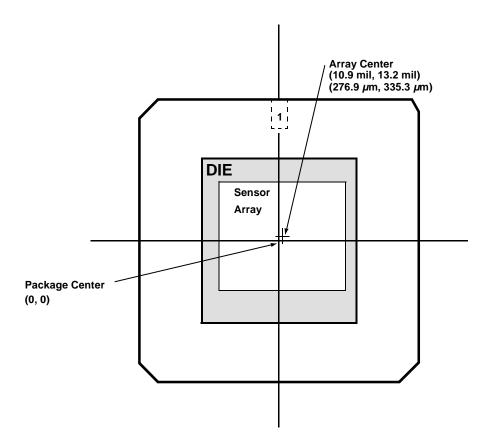

Figure 7. OV6620/OV6120 Package Outline

**Table 14. Ordering Information**

| Part Number | Description                                                    | Package    |

|-------------|----------------------------------------------------------------|------------|

| OV6620      | COLOR Image Sensor, CIF, Digital, I <sup>2</sup> C Bus Control | 48 pin LCC |

| OV6120      | B/W Image Sensor, CIF, Digital, I <sup>2</sup> C Bus Control   | 48 pin LCC |

OmniVision Technologies, Inc. reserves the right to make changes without further notice to any product herein to improve reliability, function, or design. OmniVision Technologies, Inc. does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. No part of this publication may be copied or reproduced, in any form, without the prior written consent of OmniVision Technologies, Inc.

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

#### 3. I<sup>2</sup>C Bus

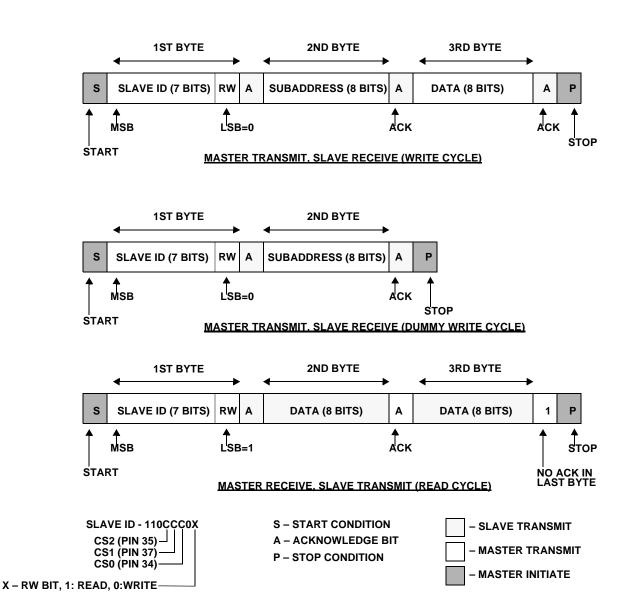

Many of the functions and configuration registers in the OV6620/OV6120 image sensors are available through the I<sup>2</sup>C interface. The I<sup>2</sup>C port is enabled by asserting the I2CB line (pin 12) through a 10K ohm resistor to

$V_{DD}$ . When the I<sup>2</sup>C capability is enabled (I2CB = 1), the OV6620/OV6120 imager operates as a slave device that supports up to 400 kbps serial transfer rate using a 7-bit address/data transfer protocol .

Figure 8. I<sup>2</sup>C Bus Protocol Format

Ī

#### 3.1 I<sup>2</sup>C Bus Protocol Format

In I<sup>2</sup>C operation, the master must perform the following operations:

- Generate the start/stop condition

- Provide the serial clock on SCL

- Place the 7-bit slave address, the RW bit, and the 8-bit subaddress on SDA

The receiver must pull down SDA during the acknowledge bit time. During the write cycle, the OV6620/OV6120 device returns the acknowledgment and, during read cycle, the master returns the acknowledgment except when the read data is the last byte. If the read data is the last byte, the master does not perform an acknowledge, indicating to the slave that the read cycle can be terminated. Note that the restart feature is not supported here.

Within each byte, MSB is always transferred first. Read/write control bit is the LSB of the first byte.

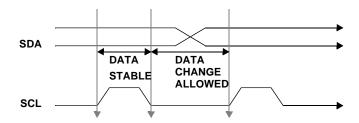

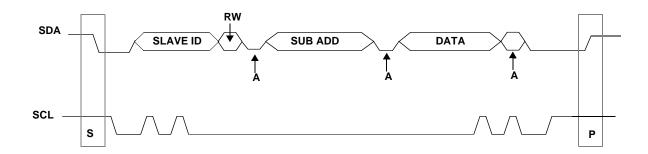

Standard I<sup>2</sup>C communications require only two pins: SCL and SDA. SDA is configured as open drain for bidirectional purpose. A HIGH to LOW transition on the SDA while SCL is HIGH indicates a START condition. A LOW to HIGH transition on the SDA while SCL is HIGH indicates a STOP condition. Only a master can generate START/STOP conditions.

Except for these two special conditions, the protocol that SDA remain stable during the HIGH period of the clock, SCL. Each bit is allowed to change state only when SCL is LOW (See Figure 9. Bit Transfer on the  $I^2C$  Bus and Figure 10. Data Transfer on the  $I^2C$  Bus below).

The OV6620/OV6120 I<sup>2</sup>C supports multi-byte write and multi-byte read. The master must supply the subaddress. in the write cycle, but not in the read cycle.

Figure 9. Bit Transfer on the I<sup>2</sup>C Bus

Figure 10. Data Transfer on the I<sup>2</sup>C Bus

24 Version 1.2 2 June 1999

#### SINGLE IC CMOS COLOR AND B/W DIGITAL CAMERAS

Therefore, the OV6620/OV6120 sensor takes the read subaddress from the previous write cycle. In multi-byte write or multi-byte read cycles, the subaddress is automatically increment after the first data byte so that continuous locations can be accessed in one bus cycle. A multi-byte cycle overwrites its original subaddress; therefore, if a read cycle immediately follows a multi-

byte cycle, you must insert a single byte write cycle that provides a new subaddress.

The OV6620/OV6120 imager can be programmed to one-of-eight slave ID addresses. Function pins CS[2:0] pins 35, 37, 34, respectively).

Table 15. Slave ID Addresses

| CS[2:0]        | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|

| WRITE ID (hex) | C0  | C4  | C8  | CC  | D0  | D4  | D8  | DC  |

| READ ID (hex)  | C1  | C5  | C9  | CD  | D1  | D5  | D9  | DD  |

The OV6620/OV6120 sensors support both single chip and multiple chip configurations. By asserting MULT (pin 47) high, the sensor can be programmed for up to 8 slave ID addresses. Asserting MULT low configures the OV6620/OV6120 imagers for single ID slave address with address C0 for writes and address C1 for reads. MULT is internally defaulted to a low condition.

In the write cycle, the second byte in  $I^2C$  bus is the sub-address for selecting the individual on-chip registers,

and the third byte is the data associated with this register. Writing to unimplemented subaddress is ignored. In the read cycle, the second byte is the data associated with the previous stored subaddress. Reading of unimplemented subaddress returns unknown.

## 3.2 Register Set

The table below provides a list and description of available  $I^2C$  registers contained in the OV6620/OV6120 image sensor.

Table 16. I<sup>2</sup>C Registers

| Subad-<br>dress<br>(hex) | Register  | Default<br>(hex) | Read/<br>Write | Descriptions                                                                                                                                                                                                                                                                                                        |

|--------------------------|-----------|------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                       | Gain[6:0] | 00               | RW             | AGC Gain Control GC[7:6] - unimplemented bit, returns 'X' when read. GC[5:0] - Storage for the current AGC Gain setting.  This register is updated automatically. If AGC is enabled, the internal control stores the optimal gain value in this register. IF AGC is not enabled, a "00" is stored in this register. |

| 01                       | Blue[7:0] | 80               | RW             | Blue Gain Control BLU[7] – "0" decrease gain, "1" increase gain. BLU[6:0] – blue channel gain balance value.                                                                                                                                                                                                        |

| 02                       | Red[7:0]  | 80               | RW             | Note: This function is not available on the OV6120 Image Sensor.  Red Gain Control  RED[7] – "0" decrease gain, "1" increase gain.  RED[6:0] – red channel balance value.                                                                                                                                           |

| 03                       | Sat       | 80               | RW             | Note: This function is not available on the OV6120 Image Sensor.  Saturation Control SAT[7:0] – saturation adjustment. "FFh"- highest, "00h"-lowest  Note: This function is not available on the OV6120 Image Sensor.                                                                                               |

| 04                       | Rsvd04    | XX               | -              | reserved                                                                                                                                                                                                                                                                                                            |

| 05                       | Cnt       | 48               | RW             | Contrast Control CTR[7:0] – contrast adjustment. "FFh"-highest, "00h"-lowest                                                                                                                                                                                                                                        |

| 06                       | Brt       | 80               | RW             | Brightness Control BRT[7:0] – brightness adjustment. "FFh"-highest, "00h"-lowest                                                                                                                                                                                                                                    |

| 07                       | Sharpness | C6               | RW             | Sharpness Control SHP[7:4] – Threshold of sharpness. Range: 0~80mV, Step: 5 mV SHP[3:0] – Sharpness control. Range: 0 ~ 8x, Step: 0.5x                                                                                                                                                                              |

| 08                       | Rsvd08    | XX               | -              | reserved                                                                                                                                                                                                                                                                                                            |

| 09                       | Rsvd09    | XX               | -              | reserved                                                                                                                                                                                                                                                                                                            |

| Subad-<br>dress<br>(hex) | Register   | Default<br>(hex) | Read/<br>Write | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|------------|------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0A                       | Rsvd0A     | XX               | -              | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0B                       | Rsvd0B     | XX               | -              | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ос                       | AWB - Blue | 20               | R/W            | White Balance Background: Blue Channel ABLU[7:6] - rsvd ABLU[5] - Sign bit. "0" - decrease background blue component "1" - increase background blue component ABLU[4:0] - White balance blue ratio adjustment  Note: This function is not available on the OV6120 Image Sensor.                                                                                                                                                                                                                                                                                                                                                |

| 0D                       | AWB - Red  | 20               | R/W            | White Balance Background: Red Channel ARED[7:6] - rsvd ARED[5] - Sign bit. "0" - decrease background red component "1" - increase background red component ABLU[4:0] - White balance red ratio adjustment  Note: This function is not available on the OV6120 Image Sensor.                                                                                                                                                                                                                                                                                                                                                    |

| 0E                       | COMR       | 0D               | RW             | Common Control R COMR[7] - Analog signal 2x gain control bit. "1" - Additional 2x gain, "0" - normal COMR[6:0] - Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OF                       | COMS       | 05               | RW             | Common Control S     COMS[7:6] - Reserved     COMS[5:4] - Black expanding level     "00" - 1.2V, "01" - 1.26V, "10" - 1.3V, "11" - 1.4V     COMS[3:2] - Set high threshold level     "00" - 1.9V, "01" - 2.0V, "10" - 2.1V, "11" - 2.2V     COMS[1:0] - Set low threshold level     "00" - 1.3V, "01" - 1.45V, "10" - 1.5V, "11" - 1.6V                                                                                                                                                                                                                                                                                        |

| 10                       | AEC        | 9A               | R              | Automatic Exposure Control $AEC[7:0] - Set exposure time$ $Interlaced: T_{ex} = T_{line} \times AEC[7:0]$ $Progressive: T_{ex} = T_{line} \times AEC[7:0] \times 2$                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 11                       | CLKRC      | 00               | R              | Clock Rate Control CLKRC[7:5] – Sync output polarity selection "00" - HSYNC=Neg, CHSYNC=Neg, VSYNC=Pos "01" - HSYNC=Neg, CHSYNC=Neg, VSYNC=Neg "10" - HSYNC=Pos, CHSYNC=Neg, VSYNC=Pos "11" - HSYNC=Pos, CHSYNC=Pos, VSYNC=Pos CLKRC[5:0] – Clock prescaler CLK = (CLK_main / ((CLKRC[5:0] + 1) x 2)) / 2                                                                                                                                                                                                                                                                                                                      |

| 12                       | СОМА       | 24               | RW             | Common Control A  COMA[7] - SRST, "1" initiates soft reset. Initiate soft reset. All registers are set to default values and chip is reset to known state and resumes normal operation. This bit is automatically cleared after reset.  COMA[6] - MIRR, "1" selects mirror image  COMA[5] - VSFR, "1" enables AGC,  COMA[4] - Digital output format, "1" selects 8-bit: Y U Y V Y U Y V  COMA[3] - Select video data output: "1" - select RGB, "0" - select YCrCb  COMA[2] - Auto White Balance "1" - Enable AWB, "0" - Disable AWB  COMA[1] - Color Bar Test Pattern: "1" - Enable color bar test pattern  COMA[0] - reserved |

|                          |            |                  |                | Note: COMA[3] is not programmable on the OV6120 Image Sensor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13                       | СОМВ       | 01               | RW             | Common Control B  COMB[7] - reserved  COMB[6] - reserved  COMB[5] - Select data format. "1" - Select 8-bit format, Y/CrCb and RGB is multiplexed to 8-bit  Y bus, UV bus is tri-stated, "0" - Select 16-bit format  COMB[4] - "1" - enable digital output in CCIR656 format  COMB[3] - CHSYNC output: "1" - Horizontal sync, "0" - composite sync  COMB[2] - "1" - Tristate Y and UV busses. "0" - enable both busses  COMB[1] - "1" - Initiate single frame transfer  COMB[0] - "1" - Enable auto adjust mode  Note: COMB[5] is not programmable on the OV6120 Image Sensor.                                                  |

| Subad-<br>dress<br>(hex) | Register | Default<br>(hex) | Read/<br>Write | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------|----------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14                       | сомс     | 00               | RW             | Common Control C COMC[7] - reserved COMC[6] - reserved COMC[5] - QCIF digital output format selection. 1 - 176x144; 0 - 352x288. COMC[4] - Field/Frame vertical sync output in VSYNC port selection: 1 - frame sync, only ODD field vertical sync; 0 - field vertical sync, effect in Interlaced mode COMC[3] - HREF polarity selection: 0 - HREF positive effective, 1 - HREF negative. COMC[2] - gamma selection: 1 - RGB Gamma on; 0 - gamma is 1. COMC[1] - reserved COMC[0] - reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 15                       | COMD     | 01               | RW             | Common Control D COMD[7] - reserved bit. COMD[6] - PCLK polarity selection. "0" OV6620 output data at PCLK falling edge and data bus will be stable at PCLK rising edge; "1" rising edge output data and stable at PCLK falling edge. When OV6620 work as CCIR656 format, COMB4=1, this bit is disable and should use PCLK rising edge latch data bus. COMD[5:1] - reserved bit. COMD[0] - U V digital output sequence exchange control. 1 - UV UV for 16-bit, U Y V Y for 8-bit; 0 - V U V U for 16Bit and V Y U Y for 8 Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16                       | FSD      | 03               | RW             | Note: COMD[0] is not programmable on the OV6120 Image Sensor.  Field Slot Division  FSD[7:2] - Field interval selection. Odd Even mode defined by FD[1:0]  000000 - disable digital data output, only output black reference level.  000001 - divide to 2 slots, HREF is active one in every 2 field/frame  000010 - divide to 4 slots, HREF is active one in every 4 field/frame  000100 - divide to 8 slots, HREF is active one in every 8 field/frame  001000 - divide to 16 slots, HREF is active one in every 32 field/frame  010000 - divide to 32 slots, HREF is active one in every 32 field/frame  100000 - divide to 64 slots, HREF is active one in every 32 field/frame  FSD[1:0]- field mode selection. Each frame consists of two fields: Odd & Even, these bits defines the assertion of HREF in relation to the two fields.  00 - OFF mode; HREF is not asserted in both fields, one exception is the single frame transfer operation (see the description for the register 13)  01 - ODD mode; HREF is asserted in odd field only.  10 - EVEN mode; HREF is asserted in even field. FD[7:2] useless. |

| 17                       | HREFST   | 38               | RW             | Horizontal HREF Start HS[7:0] - selects the starting point of HREF window, each LSB represents two pixels for CIF resolution mode, one pixels for QCIF resolution mode, this value is set based on an internal column counter, the default value corresponds to 352 horizontal window. Maximum window size is 356. see window description below. HS[7:0] programmable range is [38]- [EB], and should less than HE[7:0]. HS[7:0] should be programmable to value larger than or equal to [38]. Value larger than [EC] is invalid. See window description below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18                       | HREFEND  | EA               | RW             | Horizontal HREF End HE[7:0] - selects the ending point of HREF window, each LSB represents two pixels for full resolution and one pixels for QCIF resolution, this value is set based on an internal column counter, the default value corresponds to the last available pixel. The HE[7:0] programmable range is [39] - [EC]. HE[7:0] should be larger than HS[7:0] and less than or equal to [EC]. Value larger than [EC] is invalid. See window description below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |